Virtual Memory【NandGame編】

はじめに

いつもブログをご覧いただきありがとうございます。

ミジンコに転生したIPUSIRONです😀

Virtual Memoryレベル

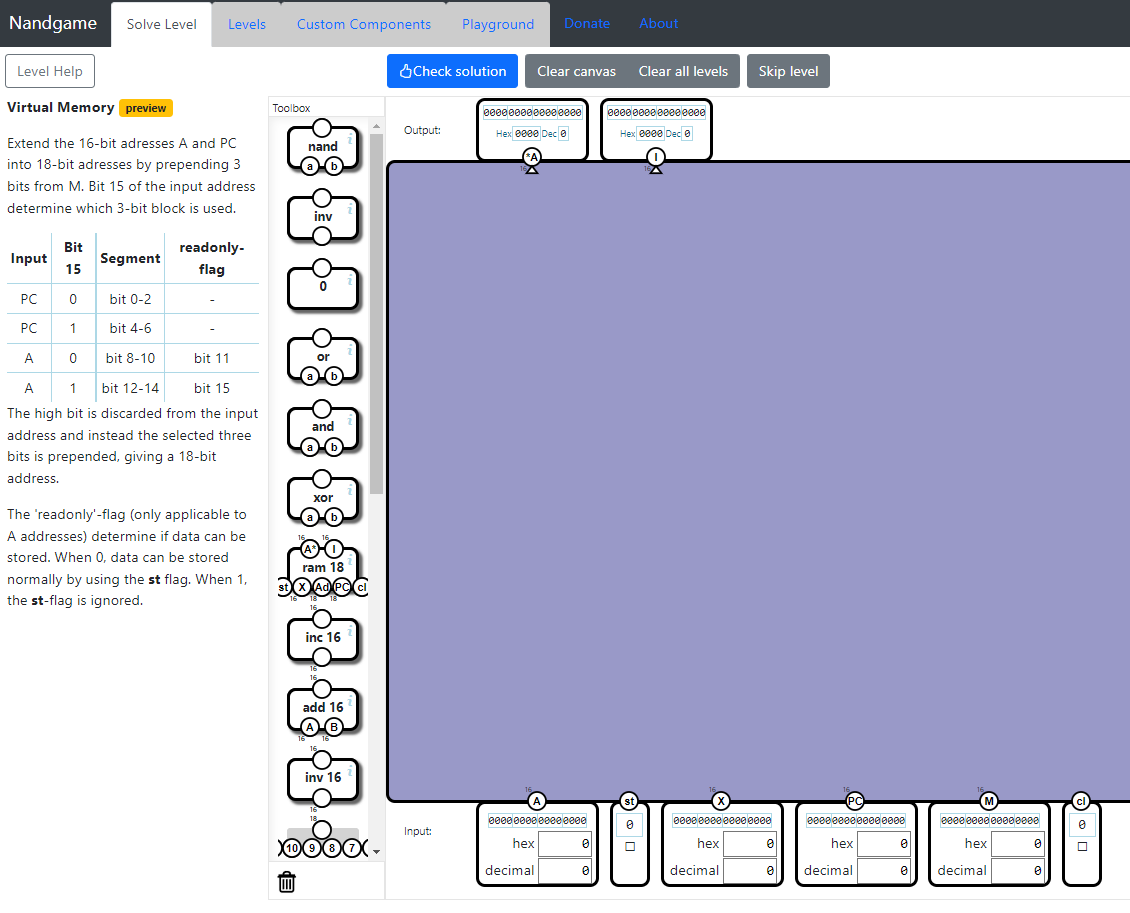

Virtual Memoryレベルのゴールは、仮想メモリーの回路を実装することです。

NandGameの仮想メモリーは次の仕組みで実現するものとします。

・入力アドレスとして、16ビット幅のアドレスAとPCがある。

・入力アドレスの15ビット目は、Mの中からどの3ビット列を抽出するかを決定する。

・入力アドレスの最上位ビット(15ビット目)は捨てられ、代わりに抽出した3ビット列を前置して、18ビットのアドレスに拡張する。

・リードオンリーフラグ(readonly-flag)は、データを保存できるか否かを決定する。アドレスAのみに適用される。

リードオンリーフラグが0の場合、stフラグをファルを使うことでデータを通常通り保存できる。対して、1の場合、stフラグは無視される。

| 入力アドレス | その15ビット目 | Mから前置するビット列セグメント | Mのリードオンリーフラグ |

|---|---|---|---|

| PC | 0 | 0~2ビット目 | - |

| PC | 1 | 4~6ビット目 | - |

| A | 0 | 8~10ビット目 | 11ビット目 |

| A | 1 | 12~14ビット目 | 15ビット目 |

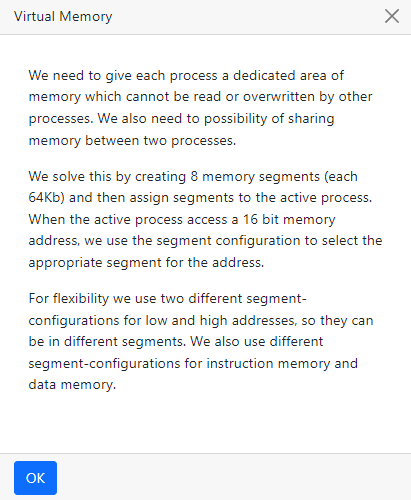

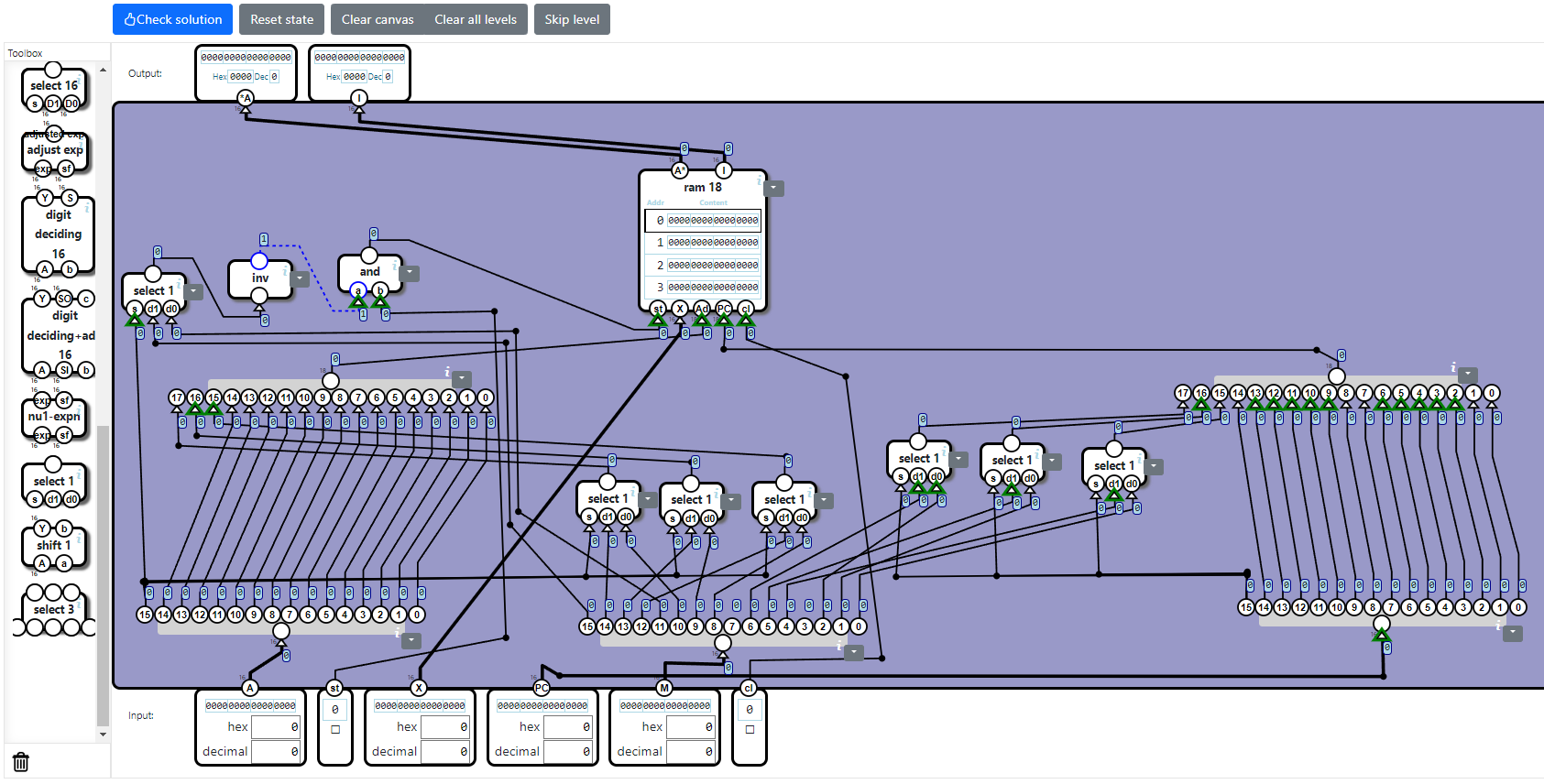

Virtual Memoryレベルを解く

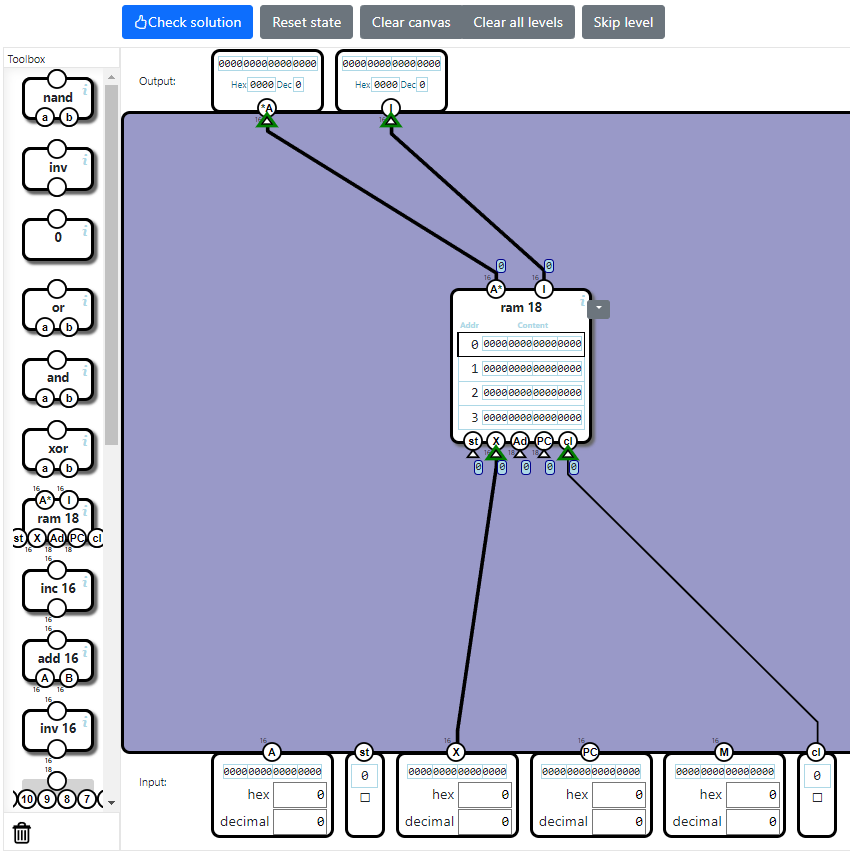

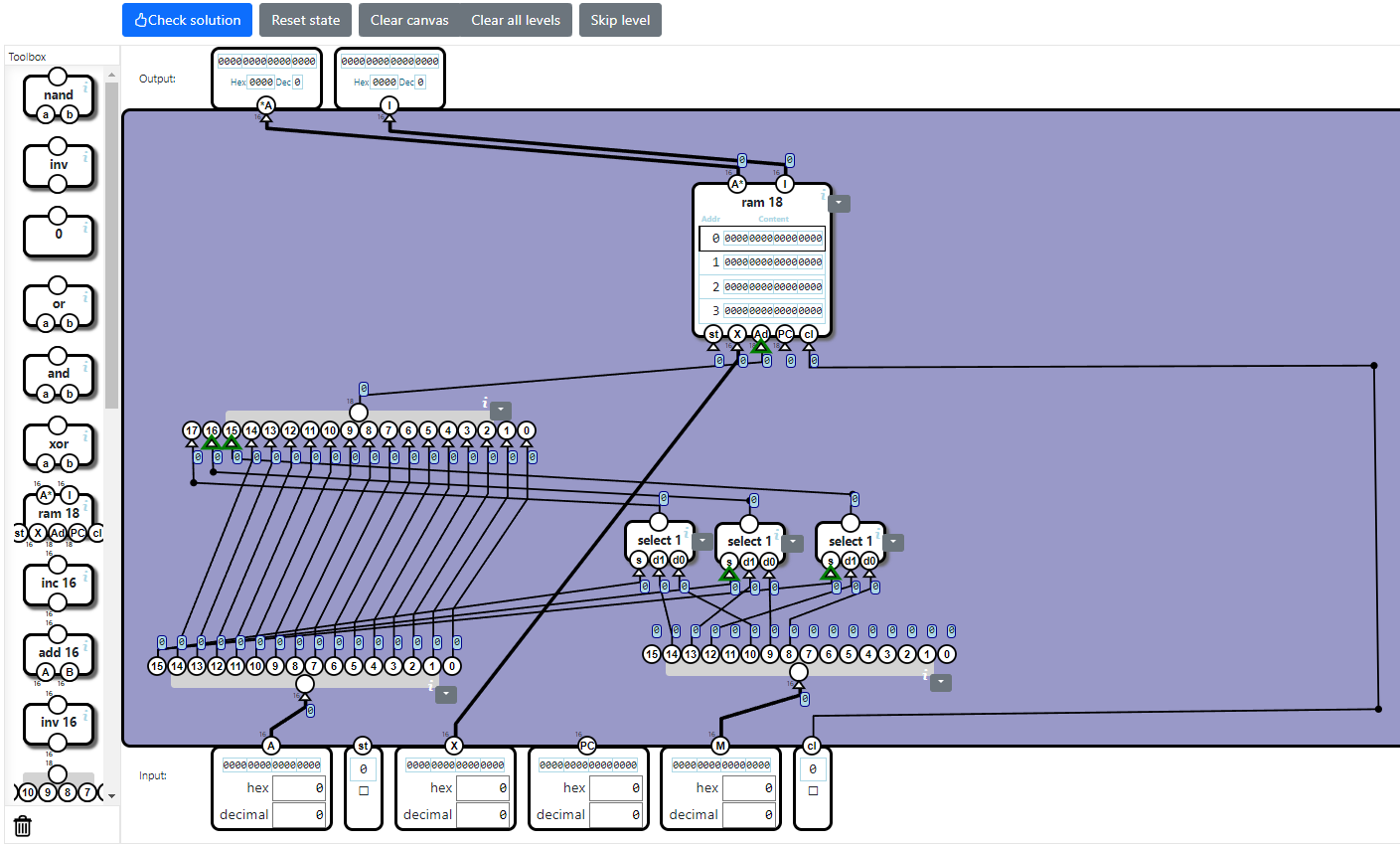

1:キャンバスの中央にram 18コンポーネントを配置します。

簡単なワイヤリングだけしておきます。

※なぜかこれだけの回路でもテストにパスしてしまいます。preview版だからでしょうか。

2:入力アドレスAの処理を実装する

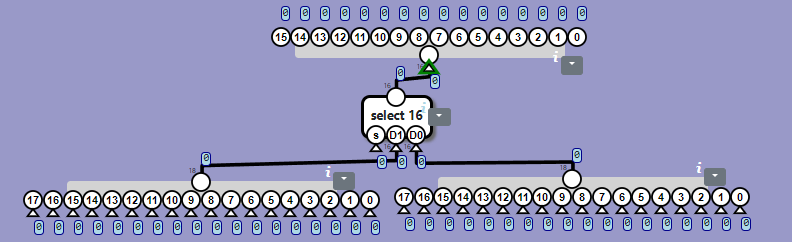

Aの15ビット目によって、Mから3ビット列を取ってくる位置が変わります。3ビットセレクターがあればよいですが、そんなものは用意されていません。1ビットセレクターを3つ並べてもよいのですが、16ビットセレクターしか用意されていません。

16ビットを使ってもよいのですが、bundlerコンポーネントやsplitterコンポーネントを使う必要になり、キャンバス上で無駄にスペースを使ってしまいます。さらに、見た目の問題だけに留まらず、回路内に使っていないNANDゲート等が増えてしまいます。

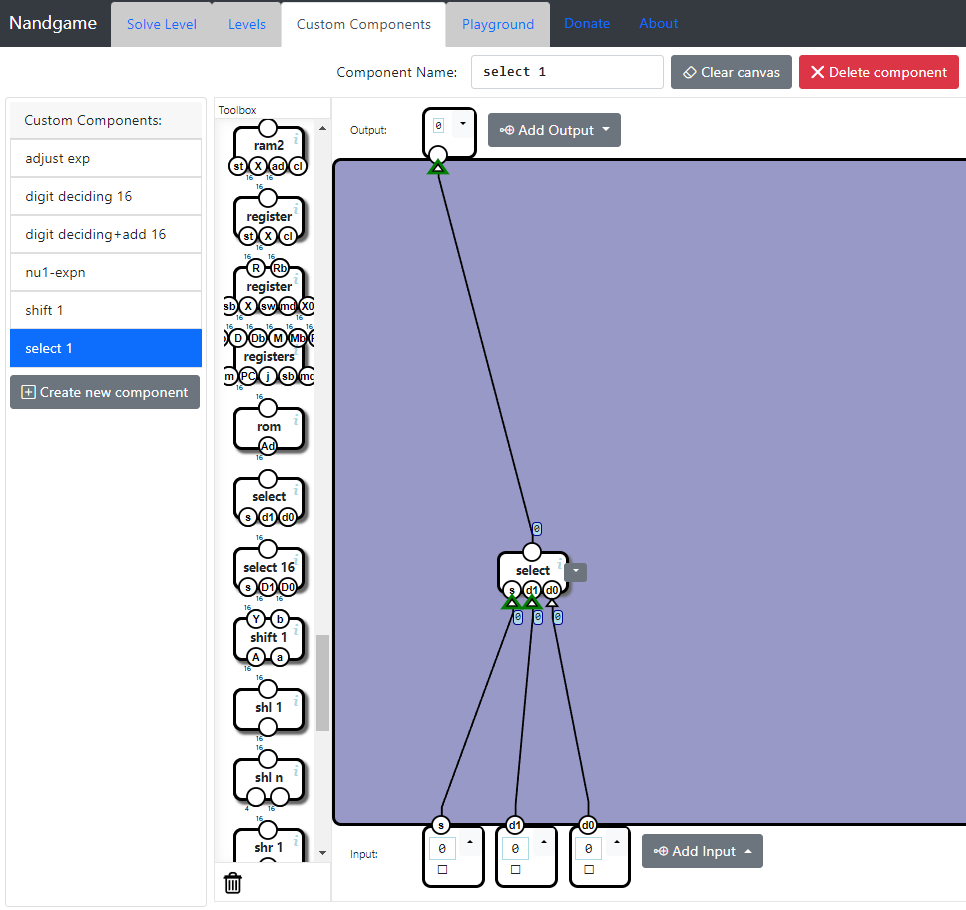

そこで、"select 1″という名称のカスタムコンポーネントを使い、当該レベルで使うことにします。

入力アドレスA(16ビット値)に3ビット列を付与して、ram 18コンポーネントのAdピン(18ビット値)に与えます。

[1]「Aの15ビット目が0」⇒「Mの8~10ビット目を抽出」⇒この3ビット列を先頭に付与

[2]「Aの15ビット目が1」⇒「Mの12~14ビット目を抽出」⇒この3ビット列を先頭に付与

PCピンは入力アドレスPC用なので、ここでは扱いません。

残っているのはstピンです。

入力アドレスAの15ビット目で、Mのどのビット目をリードオンリーフラグとして扱うのかを決めます。Aの15ビット目が0ならMの11ビット目、そうでないならMの15ビット目になります。

※この対応については当該レベルの仕様の表を参照してください。

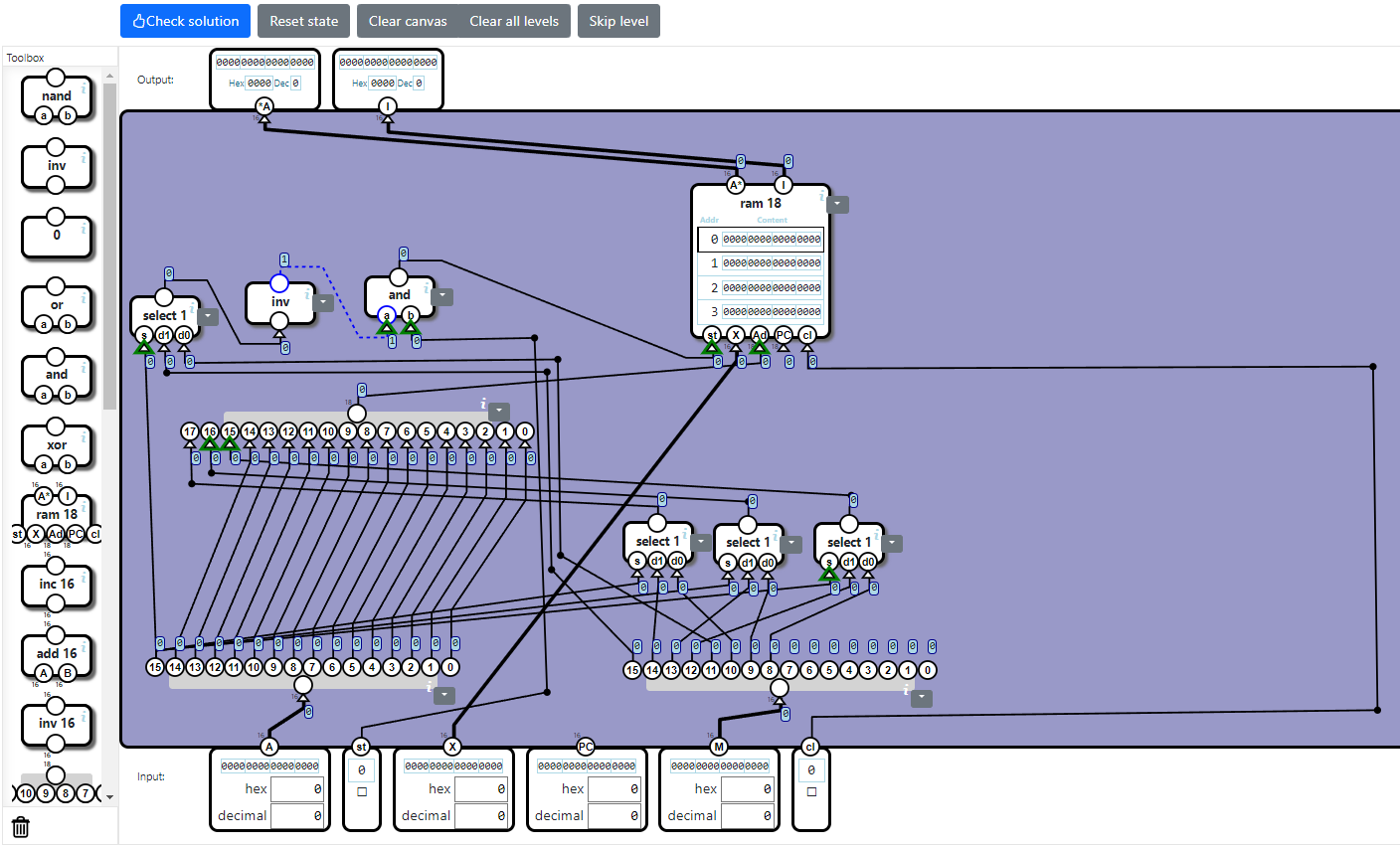

リードオンリーフラグが1なら書き込み不可、0なら書き込み可です。NOTで反転してから、入力のst端子とANDを取り、それをram 18コンポーネントのstピンに与えればよいのです。

3:入力アドレスPCの処理を実装する

PCについてもAと同様に考えます。リードオンリーフラグを考える必要がない分、楽かもしれません。

入力アドレスPC(16ビット値)に3ビット列を付与して、ram 18コンポーネントのPCピン(18ビット値)に与えます。

[1]「PCの15ビット目が0」⇒「Mの0~2ビット目を抽出」⇒この3ビット列を先頭に付与

[2]「PCの15ビット目が1」⇒「Mの4~6ビット目を抽出」⇒この3ビット列を先頭に付与

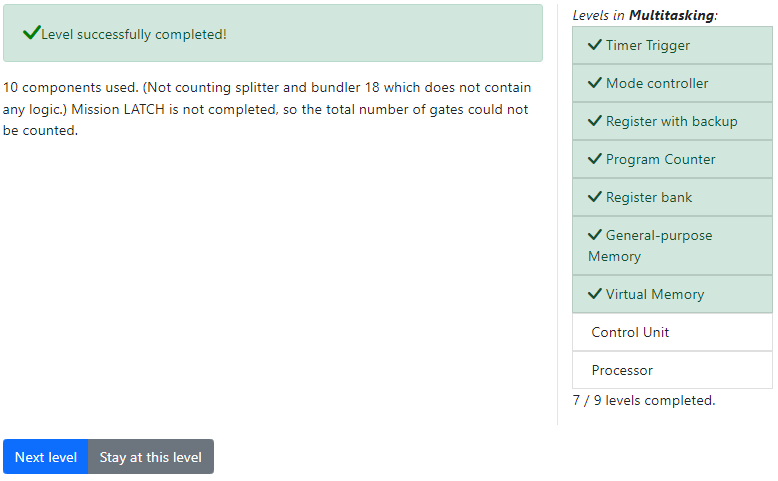

4:テストする

テストにパスすると、クリアになります。