Registers【Turing Complete編】

はじめに

いつもブログをご覧いただきありがとうございます。

ミジンコに転生したIPUSIRONです😀

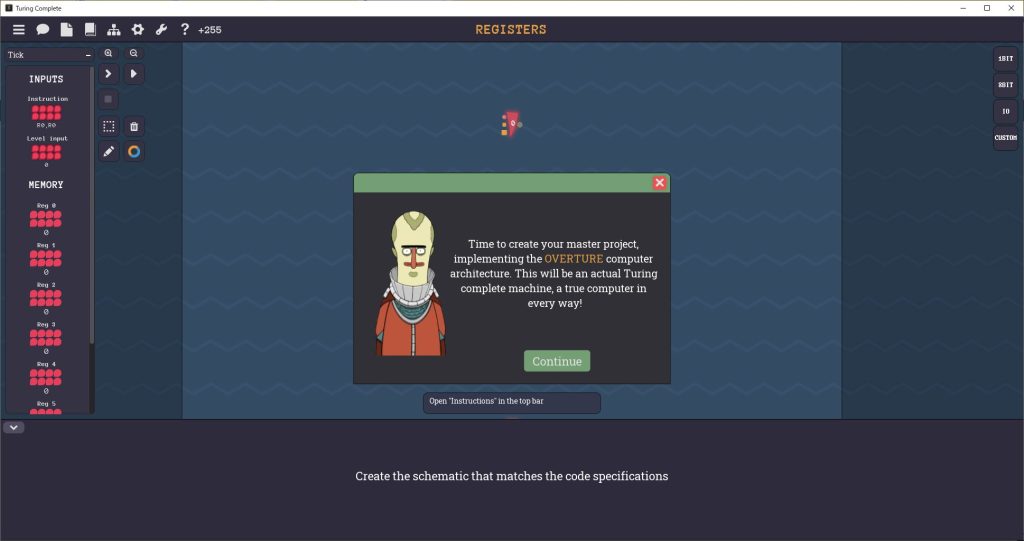

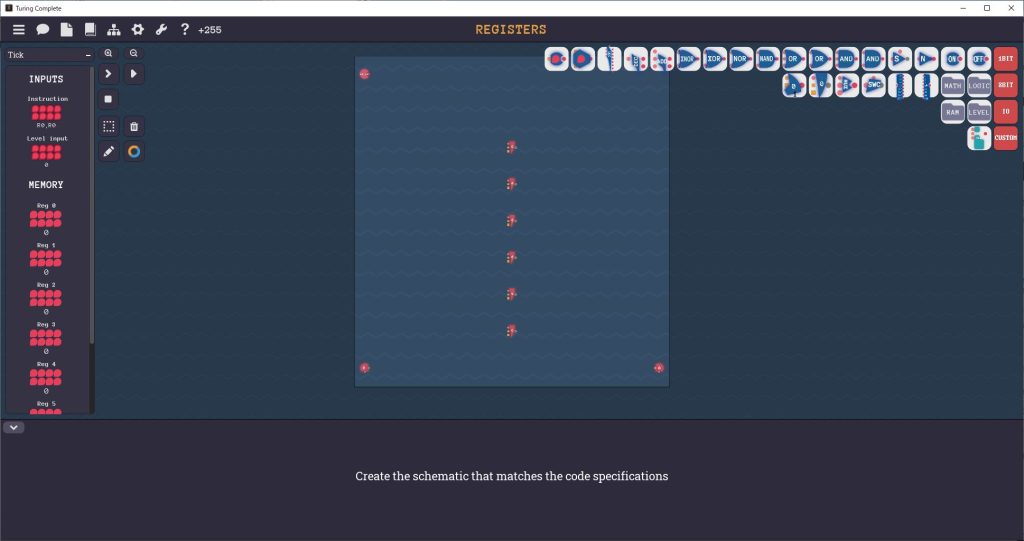

Registersステージ

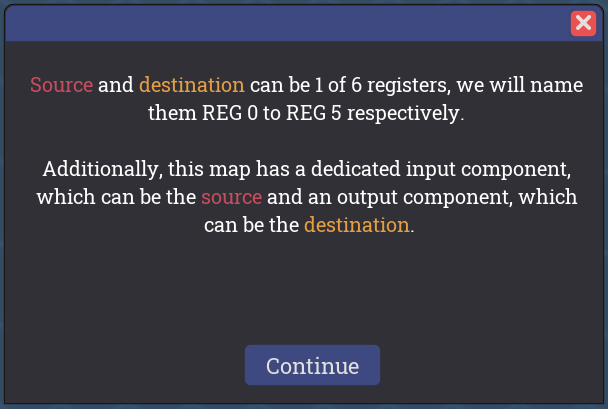

このステージのゴールは、1バイトデータをレジスター間でコピーする回路を組むことです。

入力からレジスターへ、レジスターから出力へというパターンもあります。

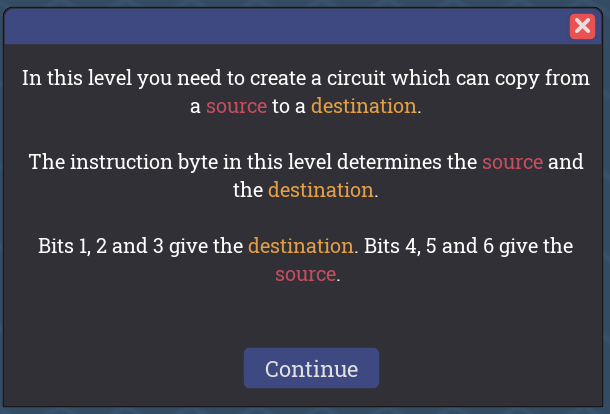

仕様を確認する

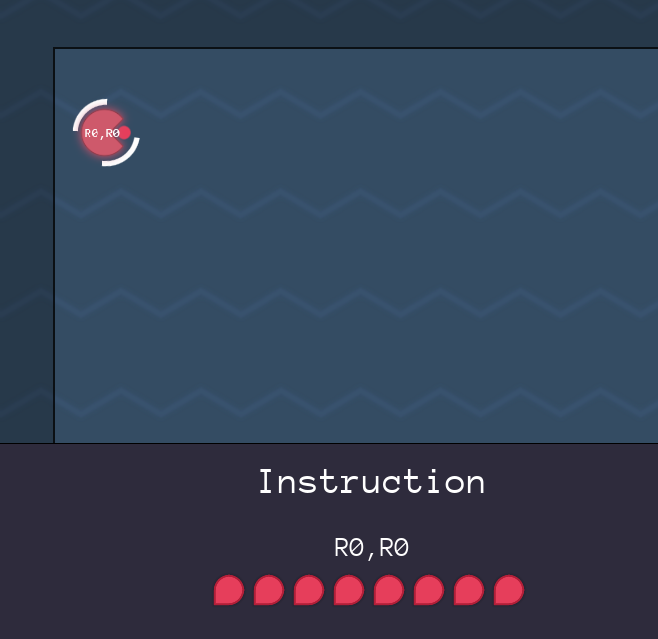

左上のアイコン一覧から歯車(Instructions)アイコンを押します。

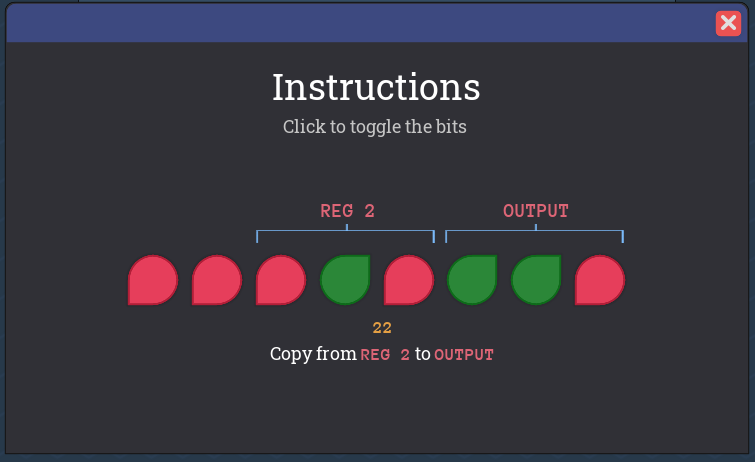

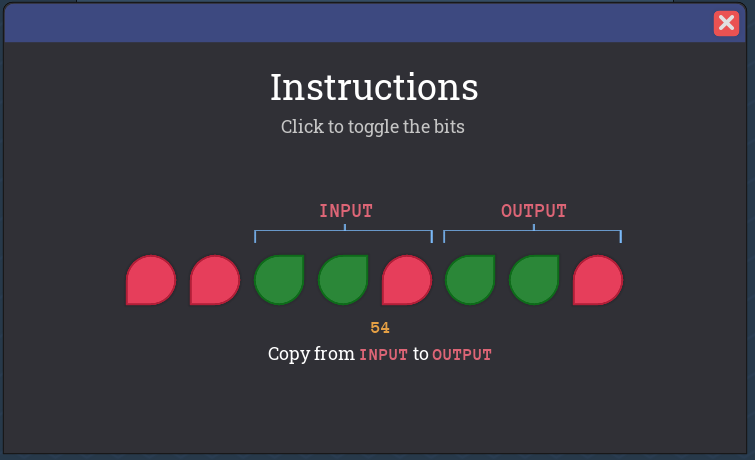

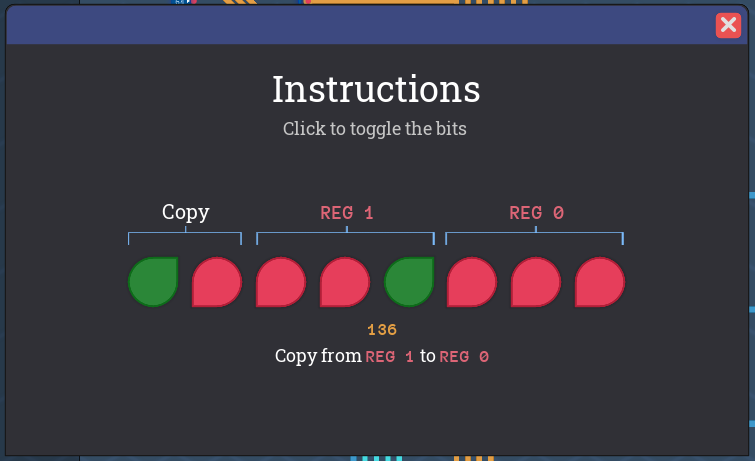

Instructions画面が表示されます。

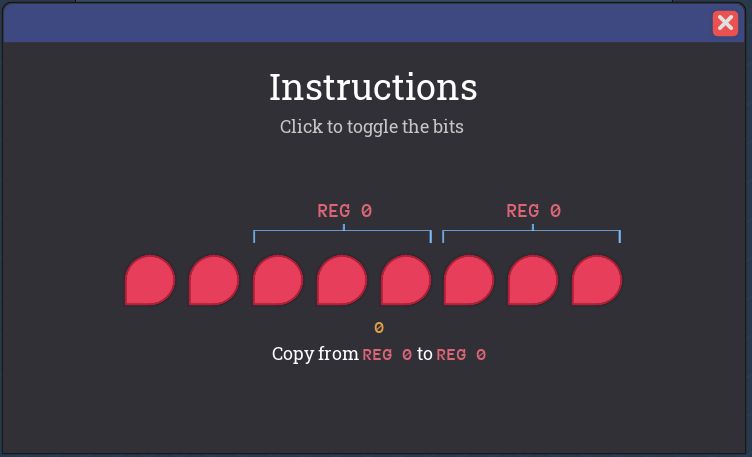

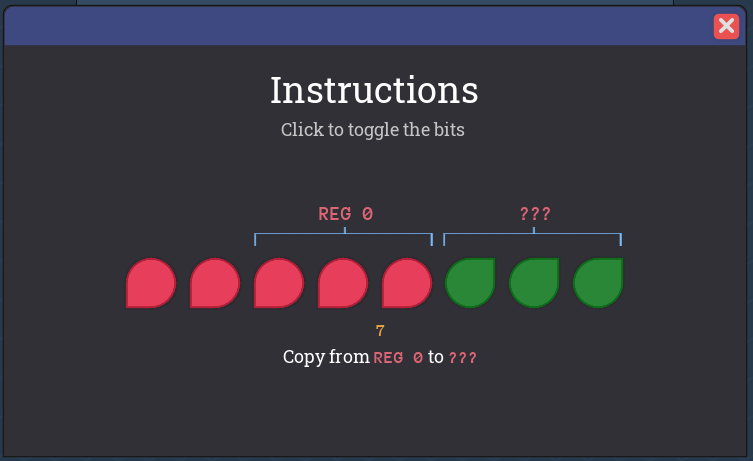

Instructionは8ビットですが、このステージではコピー処理をするモードに固定されています。

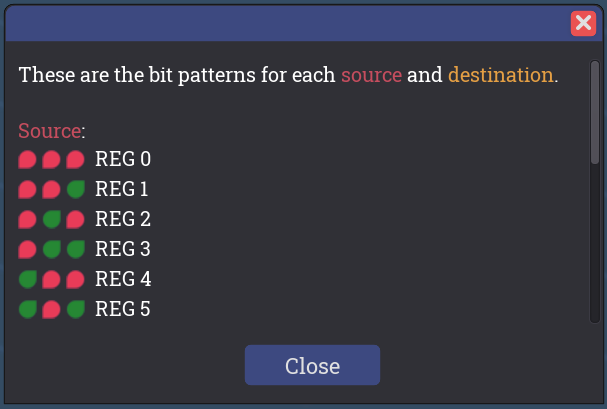

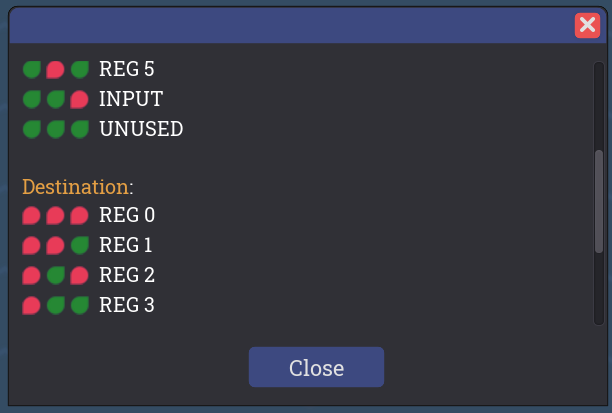

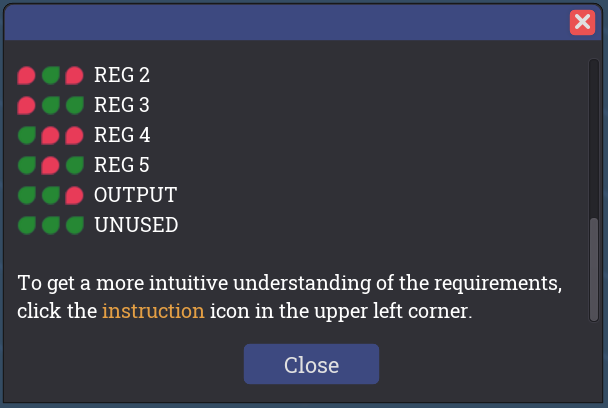

Instructions画面においてビットを操作することで、どこからどこへのコピーかを調べられます。

上位2桁は使わず、下位6桁のみを使用します。

※厳密には、このステージにおいて上位2桁がONになっても無視されます。それ以外のモードに切り替わることは想定しません。

例えば、全部OFFの状態だと、下に"Copy from REG 0 to REG 0″と表示されます。これはInstructionが0000 0000bなら、REG 0からREG 0にコピーすることを意味します。

皆さんは実際にビットをON・OFFして、挙動を確認してください。以下に、Instructionの表を載せておきます。

※ビット列はよく4桁区切りで表現されますが、ここではInstructionにおけるコピー元とコピー先が明確になるように区切ります。表現を買えただけで、本質的に何かが変わるわけではありません。または「*」は0と1のどちらでもよいことを意味します。

| Instruction | コピー元 | コピー先 |

|---|---|---|

| ** 000 000b | REG 0 | REG 0 |

| ** 000 001b | REG 0 | REG 1 |

| ** 000 010b | REG 0 | REG 2 |

| ** 000 011b | REG 0 | REG 3 |

| ** 000 100b | REG 0 | REG 4 |

| ** 000 101b | REG 0 | REG 5 |

| ** 000 110b | REG 0 | OUTPUT |

| ** 000 111b | REG 0 | ??? |

| ** 001 000b | REG 1 | REG 0 |

| ** 010 000b | REG 2 | REG 0 |

| ・・・ | ・・・ | ・・・ |

| ** 101 000b | REG 5 | REG 0 |

| ** 110 000b | INPUT | REG 0 |

| ** 111 000b | ??? | REG 0 |

※ここでは「REG 0⇒*」「*⇒REG 0」のパターンだけに注目しましたが、「REG 2⇒REG 3」などのパターンも同様に考えられます。

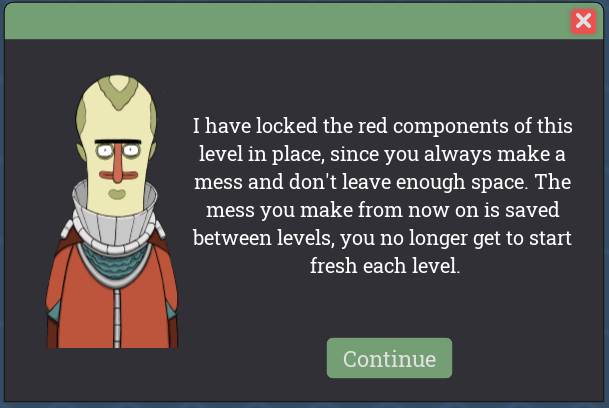

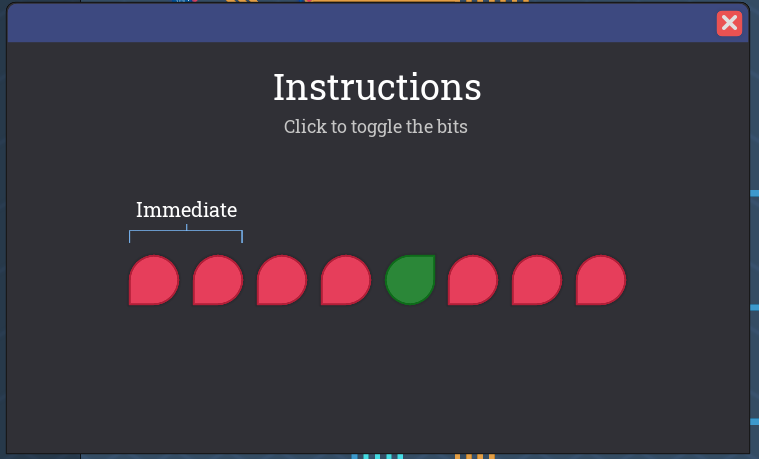

クリア後にInstructions画面の挙動が変わる

この問題をクリアしてからInstructions画面を表示すると、以降の問題に合わせたInstruction画面になってしまいます。

※おそらくバグです。

上位2桁がImmediateの役割を持つようになります。この問題では上位2桁は使わずに常にコピー処理になりますので、最上位のみをONにしてCopyモードにしてからInstructionビット列を解読してください。

最初から回路に配置されているコンポーネント

| 位置 | コンポーネント | 仕様 |

|---|---|---|

| 左上 | Instruction端子 | 【入力用】 8ビット列のInstructionを指定することで、回路に処理を指示できる。 Instructionはどこからどこへコピーするという内容。 具体的なInstructionの定義は前述した。 |

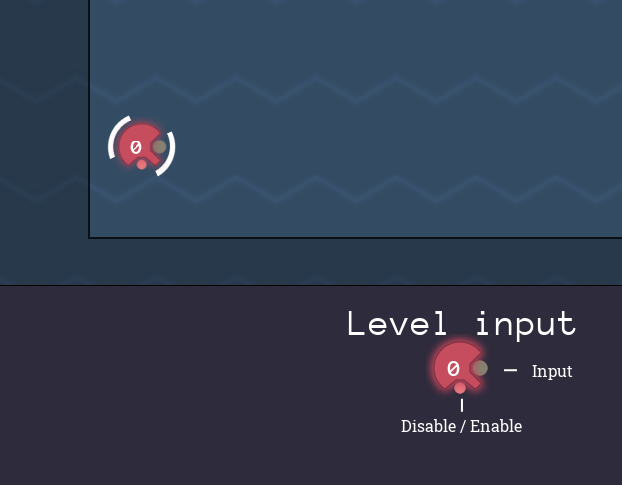

| 左下 | Level input端子 | 【入力用】 ・Inputピン:転送対象の1バイトデータ。 ・Disable/Enableピン:1ビット 意味的に考えると、回路内のレジスター間でデータをコピーしている間はOFF(Disable)にする。バイトデータを回路に入力するときだけ、ON(Enable)にする。 |

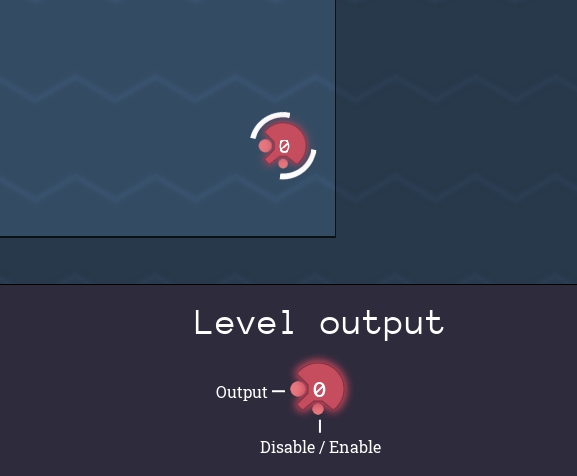

| 右下 | Level output端子 | 【出力用】 ・Outputピン:対象の1バイトデータ。 ・Disable/Enableピン:1ビット 意味的に考えると、回路内のレジスター間でデータをコピーしている間はOFF(Disable)にする。バイトデータを回路から出力するときだけ、ON(Enable)にする。 |

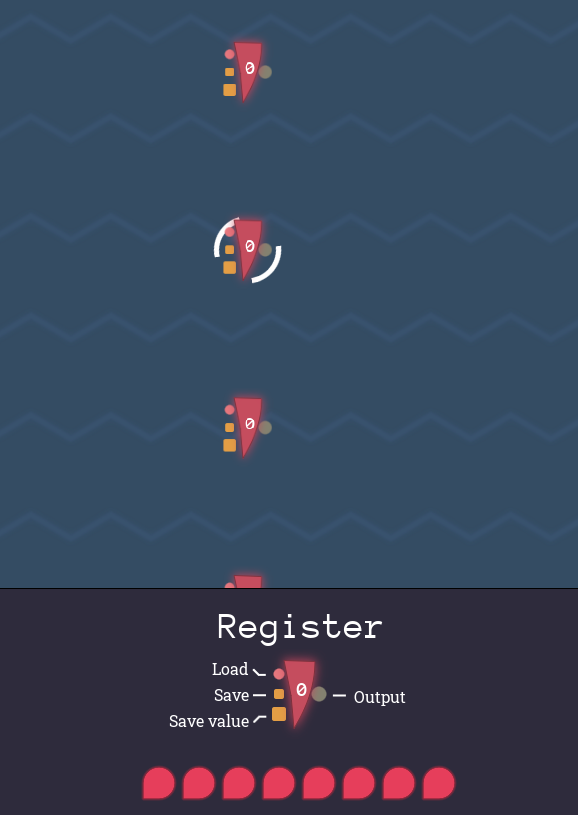

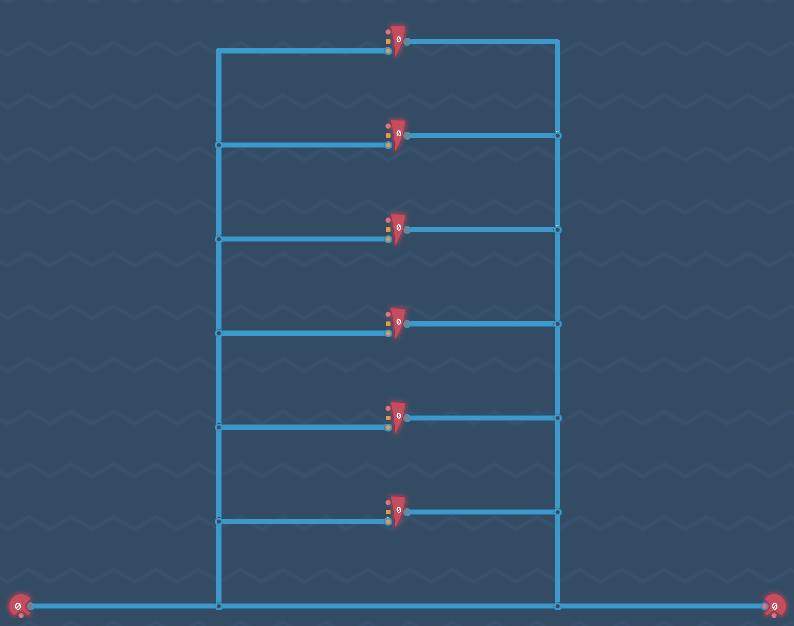

| 中央 | Registerコンポーネント | 8 Bit Registerが6個並んでいる。 一番上がレジスターREG 0、一番下がREG 5に対応する。 8 Bit Registerの入出力は次の通り。 【入力】 ・Loadピン:1ビット。ONなら、記憶しているデータをロードして出力。 ・Saveピン:1ビット。ONなら、データを記憶。 ・Save valueピン:1バイト。コピー対象のバイトデータが扱う。 【出力】 ・Outputピン:1バイト。 |

CPUアーキテクチャーの解説によく登場する、ALU、レジスター、メモリー、場合によってデータキャッシュやインストラクションキャッシュなどのブロック配置図を想像するとよいでしょう。

今回のステージのキャンバスはやたら広いのは、これがCPUの骨格的な存在になるためです。

ゆくゆくは隙間に別の回路(プログラムカウンターとか)が組み込まれていくことを想像できます。

Registersステージを解く

1:設計ポイントを再考する

この問題では次の観点に着目すれば、回路の設計がスムーズにいくはずです。

・Instructionの仕様を見ると、2進数が入力先・出力先を決定している。

・入出力の対象として、Level input端子、Level output端子、6個のレジスターが登場する。それぞれにDisable/EnableピンやLoadピン・Saveピンがあるので、これをどうやってつなぐかを考える。

以上の2つから、Instructionのビット列をマルチプレクサーで分離して、対象コンポーネントのDisable/EnableピンやLoadピン・Saveピンにつなげばよさそうです。

2:バイトデータが転送されるワイヤーを配線する

先に簡単なことから解決しておきましょう。

コピー対象のデータは1バイト共通です。つまり、8ビット幅のバスと考えてよく、全コンポーネントを直接接続してもよいことになります。

※つながっていても、ロード状態やセーブ状態でなければ無視されるからです。

3:Instructionを分解して、コピー元とコピー先のワイヤーを確定する

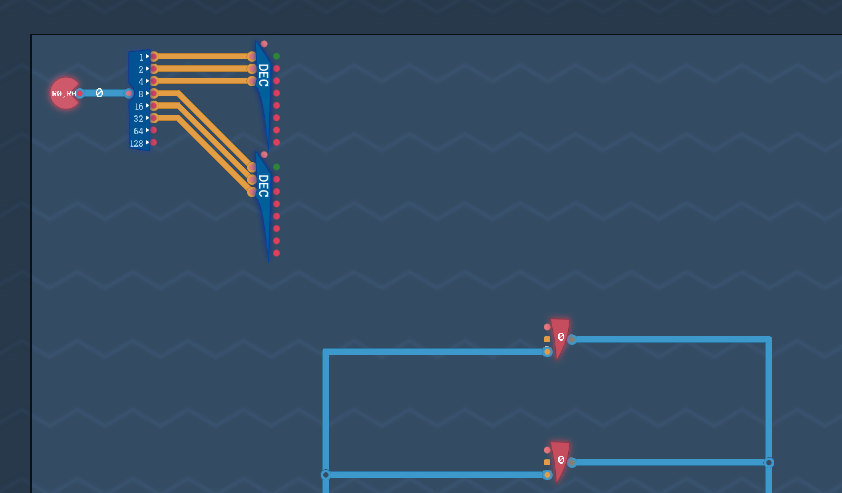

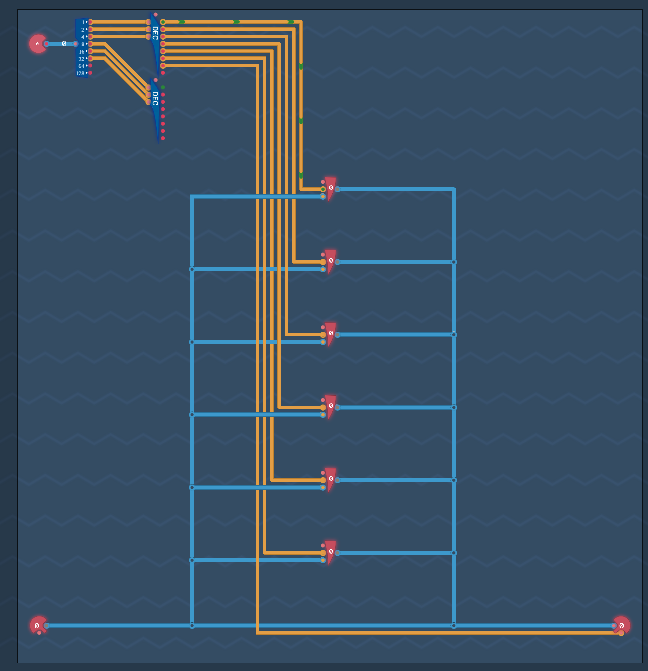

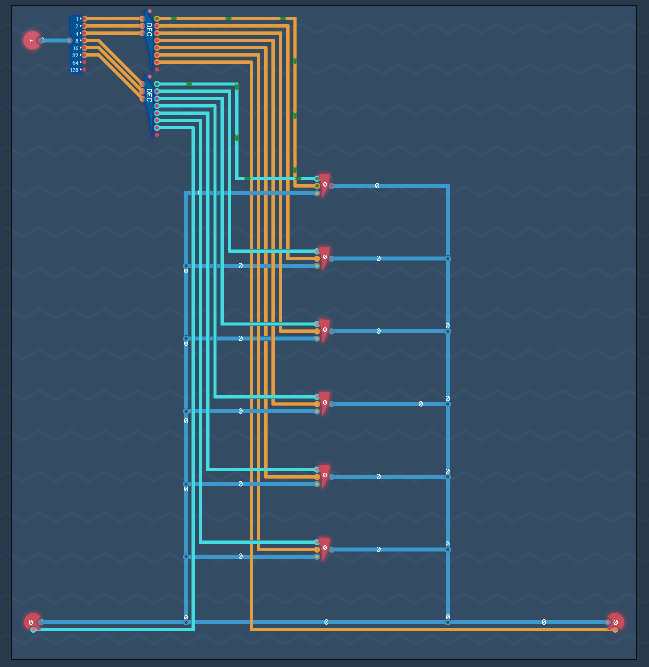

Instruction端子からは1バイトのInstructionが来るので、まずは8 Bit Splitterで分離します。その後、コピー元の3ビット、コピー先の3ビットに対して、3 Bit decoderをつなげます。

4:コピー先の確定処理のためにワイヤリングする

上の3 Bit decoderがコピー先(レジスターあるいはLevel output端子)を決定するものになります。

3 Bit decoderの出力は1ビットが8つありますが、上からREG 0、REG 1、・・・、Level output端子に対応します。

特に、Level output端子のDisable/Enable端子がONになったときに、この端子が有効になります。つまり、3 Bit decorderの7桁目と直結します。

後は、各レジスターのLoadピンとSaveピンのどちらを使うのかという点が問題です。

結論からいうと、Saveピンを使います。コピー先はデータを記憶する側だからです。

以上を踏まえて配線すると次のようになります。

5:コピー元の確定処理のためにワイヤリングする

コピー元の確定処理についても、同様の考えでワイヤリングします。

コピー元はデータをロードする側なので、レジスターのLoadピンが使われます。

6:テストする

テストがパスすると、ステージをクリアします。