Latch【NandGame編】

はじめに

いつもブログをご覧いただきありがとうございます。

ミジンコに転生したIPUSIRONです😀

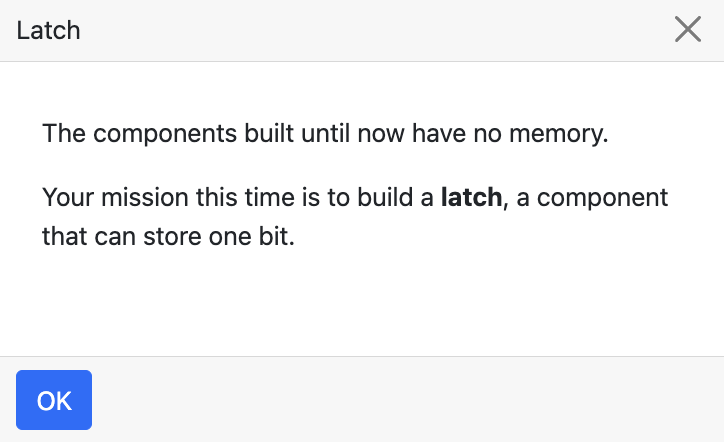

Latchレベル

Latchレベルのゴールは、1ビットラッチを組むことです。

ラッチはビットを記憶し、出力します。つまり、1ビットラッチは1ビットを記憶したり出力したりできます。

入力にはdとstがあります。st(ストア)が1のとき、dの値を記憶(ストア)し、出力します。一方、stが0のときは、dの値を無視し、保持している値をそのまま出力します。

入出力表を表現するために、ビット値を代入して保持できる変数outを導入しています。

Latchレベルを解く

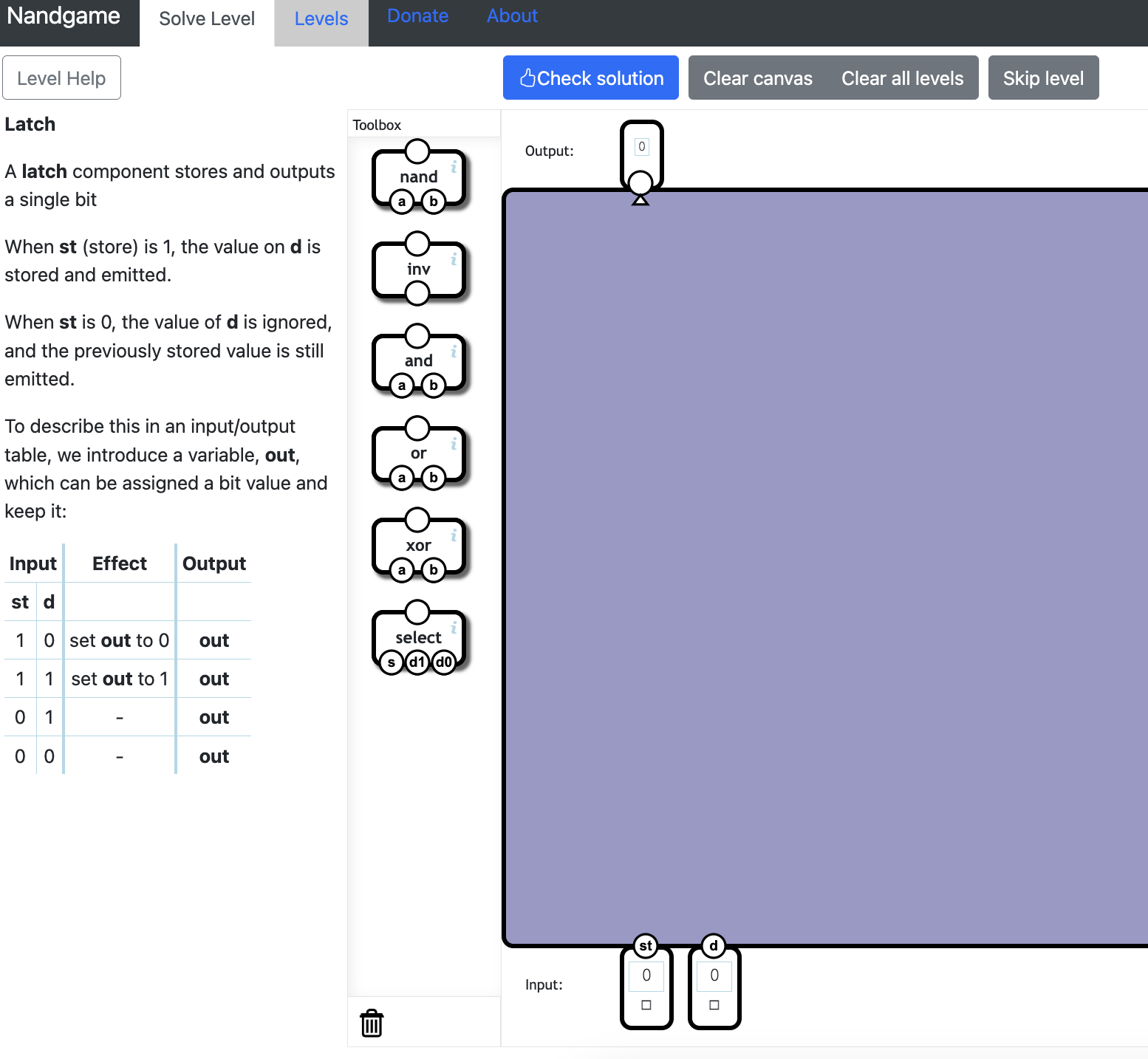

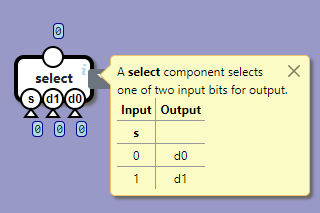

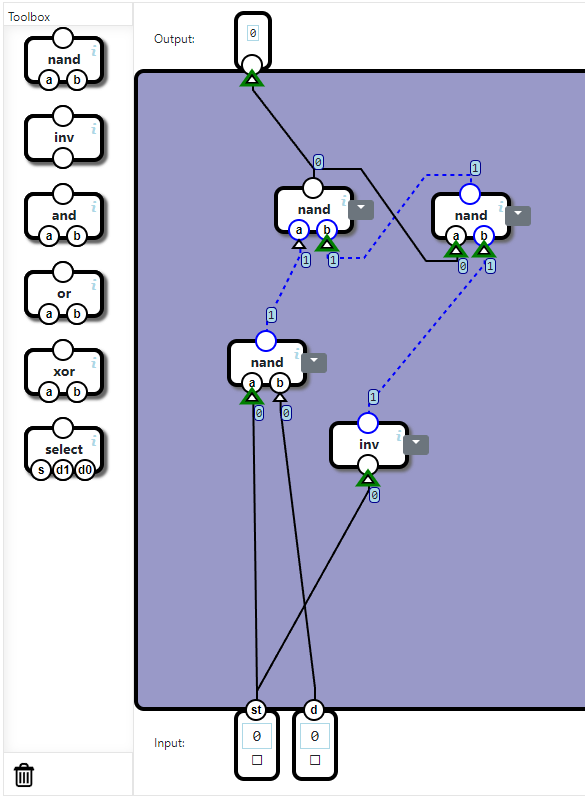

2-1セレクター(selectコンポーネントとして与えられている)を使えば、1ビットラッチを作れます。

st端子をセレクターのsピンに接続して、どちらのルートを通すかを制御させます。

まずは簡単なst=1の場合から考えます。

・「st=1」⇒「s=1」⇒「d1ピンとselectの出力のルートが開通」⇒「d1ピンの値(d端子に与えられたデータそのもの)がそのまま出力」

次にst=0の場合を考えます。過去のビット値を保持する必要があるので、selectコンポーネントの出力をd0にループさせます。こうすることで、「出力⇒入力⇒出力⇒・・・」という連続の動作によって、擬似的に1ビットを保持しているような状況になります。

・「st=0」⇒「s=0」⇒「d0ピンとselectの出力のルートが開通」⇒「過去のデータを出力」(d端子に与えられたデータは無視)

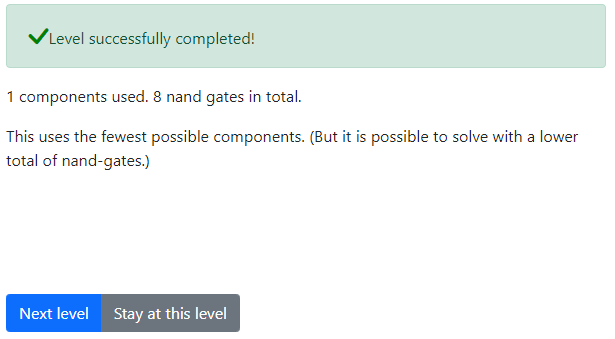

この回路は1つのコンポーネントを使い、内部的には8個のNandゲートで構成されます。

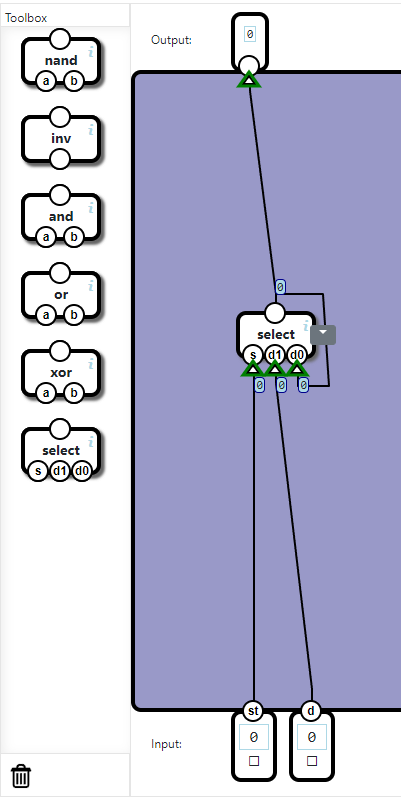

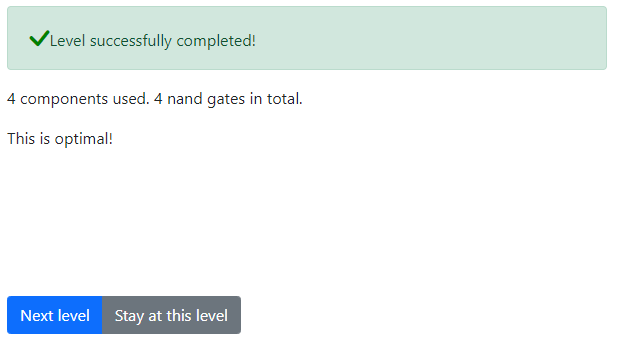

NANDのペアを使う【別解】

上記の回路は不正解扱いになったようです。

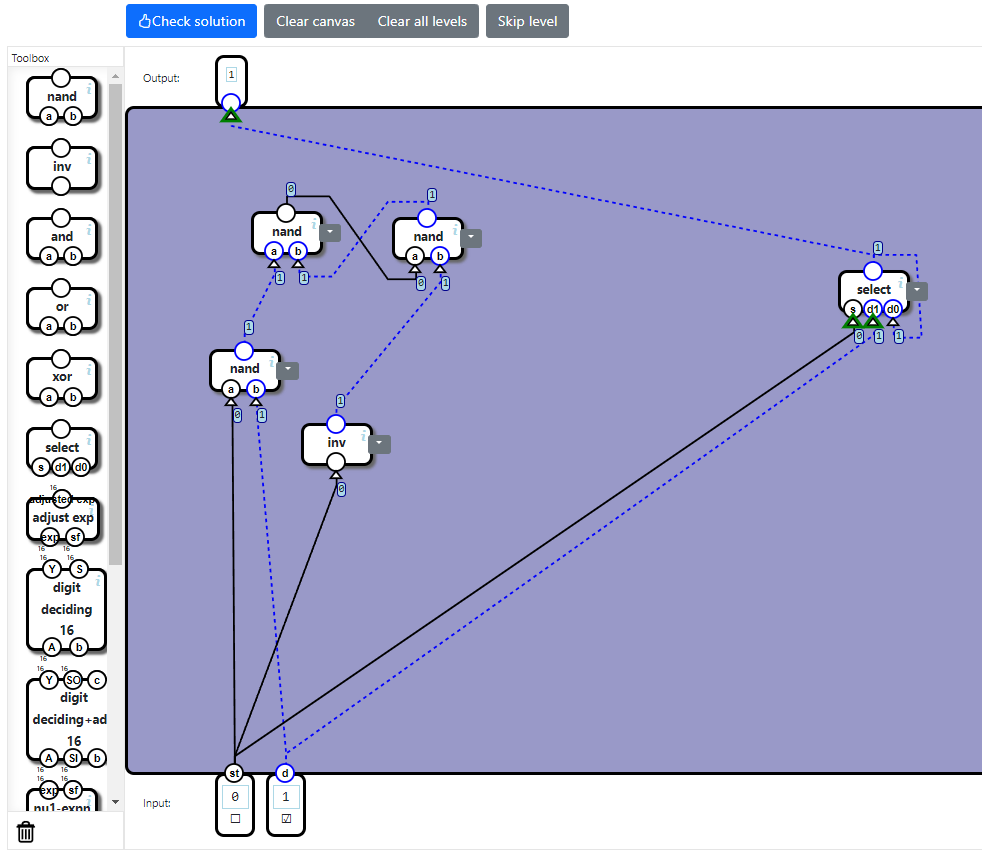

キャンバスに「最初の回路」と「別解の回路」を並べて、手動でテストすると出力が一部違うことがわかります。

「(st,d)=(0,0)⇒(1,0)⇒(1,1)⇒(0,1)」と遷移させたとき、別解の回路の出力は0ですが、最初の回路の出力は1になっています。

別解となりうる回路を並べて、挙動を確認するテクニックは意外と有効です。

ただし、出力端子にはワイヤリングできるのは1本なので、その点だけは留意する必要があります。