1 Bit Decoderと3 Bit Decoder【Turing Complete編】

目次

はじめに

いつもブログをご覧いただきありがとうございます。

ミジンコに転生したIPUSIRONです😀

いきなり3ビットデコーダーの回路図を見ても、配線が複雑に見えます。

また、正解の回路図をそのままTuring Completeの回路に置き換えるだけでは学習効果があまり期待できません。

ここでは頭を使って3ビットデコーダーを作成する方法を方法を紹介します。

頭を使うといってもちょっとだけなので安心してください。

デコーダー

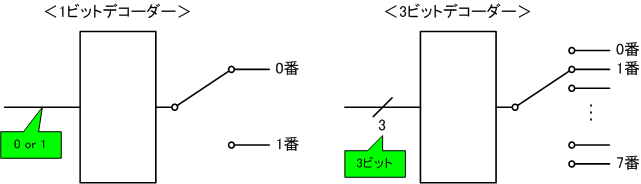

デコーダー(decoder)とは、エンコード(符号化すること)と反対の機能を持つ回路です。

2進に符号化されたコードが入力に与えられると、その組み合わせに対応する信号が、多数の出力端子のうちの1つに出力します。

言葉ではわかりにくいですが、図にすると一目瞭然です。

用途を明確にするために、用途を名称につけることがあります。

例えば、アドレスデータを解読して制御信号するデコーダーはアドレスデコーダー、何の命令かを解読するデコーダーはインストラクションデコーダーと呼ばれます。

入出力のビット数を明確にする場合は「入力ビット値x出力ビット値」と表記する

| 入力ビット値 | 出力ビット値 | よくある表記 | 入出力を明確した表記 |

|---|---|---|---|

| 1 | 2 | 1ビットデコーダー | 1×2ビットデコーダー |

| 2 | 4 | 2ビットデコーダー | 2×4ビットデコーダー |

| 3 | 8 | 3ビットデコーダー | 3×8ビットデコーダー |

| 4 | 16 | 4ビットデコーダー | 4×16ビットデコーダー |

| 5 | 32 | 5ビットデコーダー | 5×32ビットデコーダー |

| 6 | 64 | 6ビットデコーダー | 6×64ビットデコーダー |

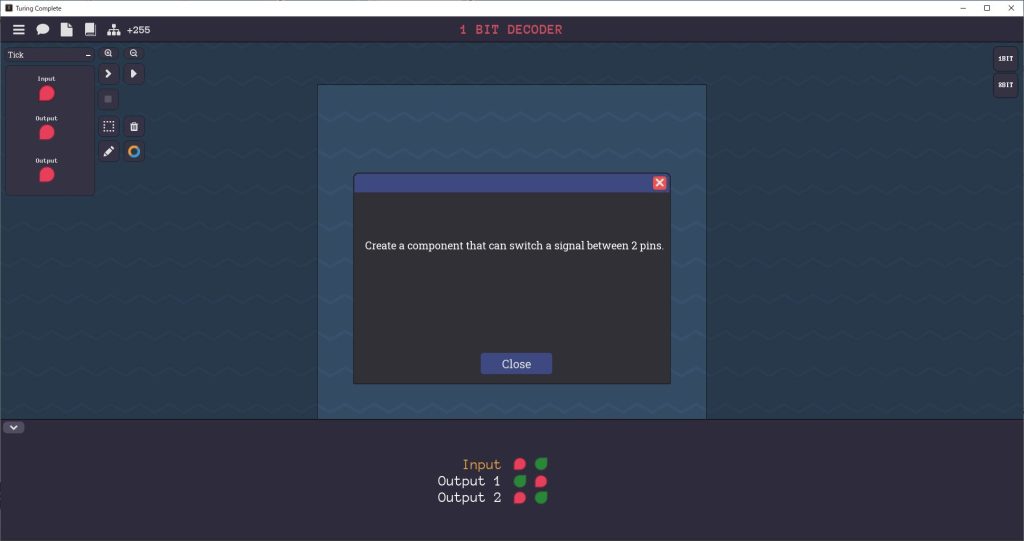

1 Bit Decoderステージ

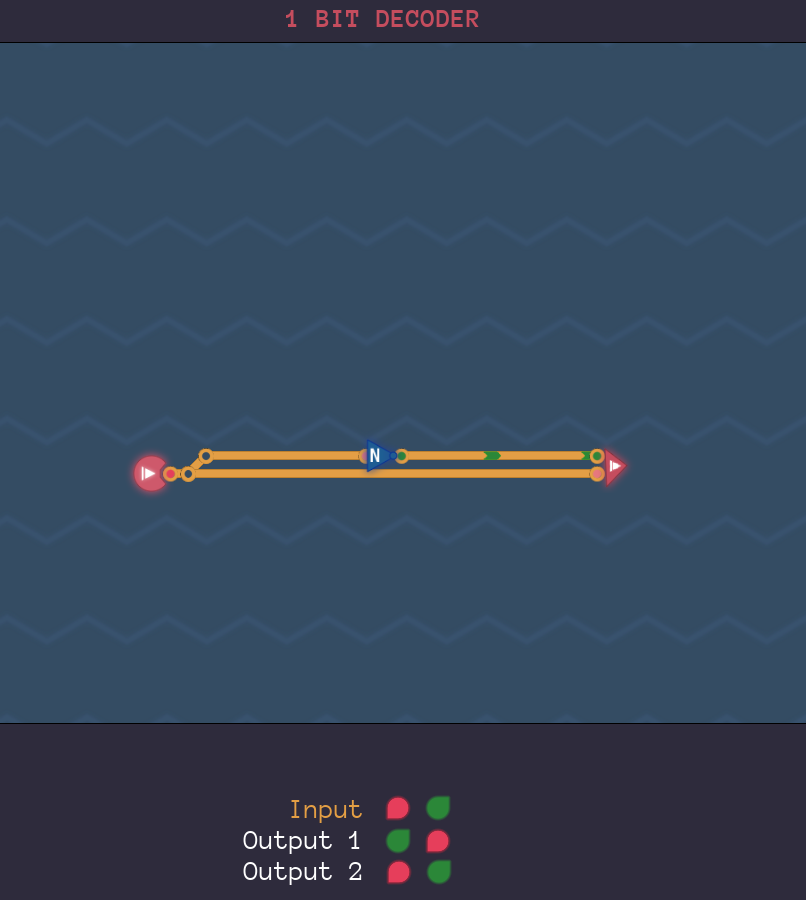

入力の電圧レベルによって出力先を切り替える回路を組む問題です。

【入力】

・Input:1ビット

【出力】

・Output 1:1ビット。InputがOFFのときにON、それ以外はOFF。

・Output 2:1ビット。InputがONのときにON、それ以外はOFF。

1 Bit Decoderステージを解く

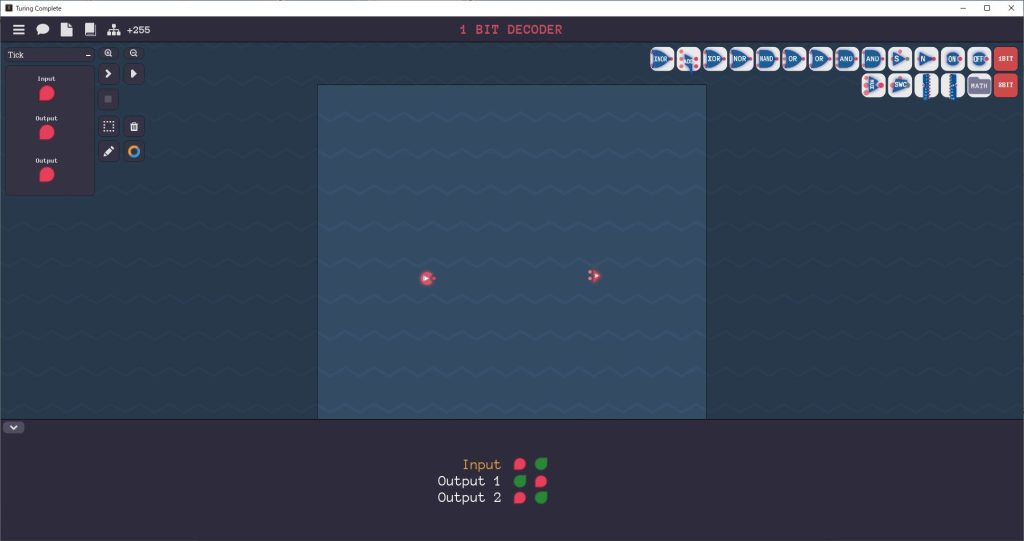

2つの出力の片方は入力ビットと同一、もう片方がその反転ビットとなる回路を組むだけです。

2つの出力から伸びるワイヤーには途中にNOTゲートがあるはずと推測できます。

後は単純に入力から伸びるワイヤーを分岐して、出力から伸びている2本のワイヤーと連結すればよいのです。

クリアすると、1 Bit decoderコンポーネントがアンロックします。

3 Bit Decoderステージ

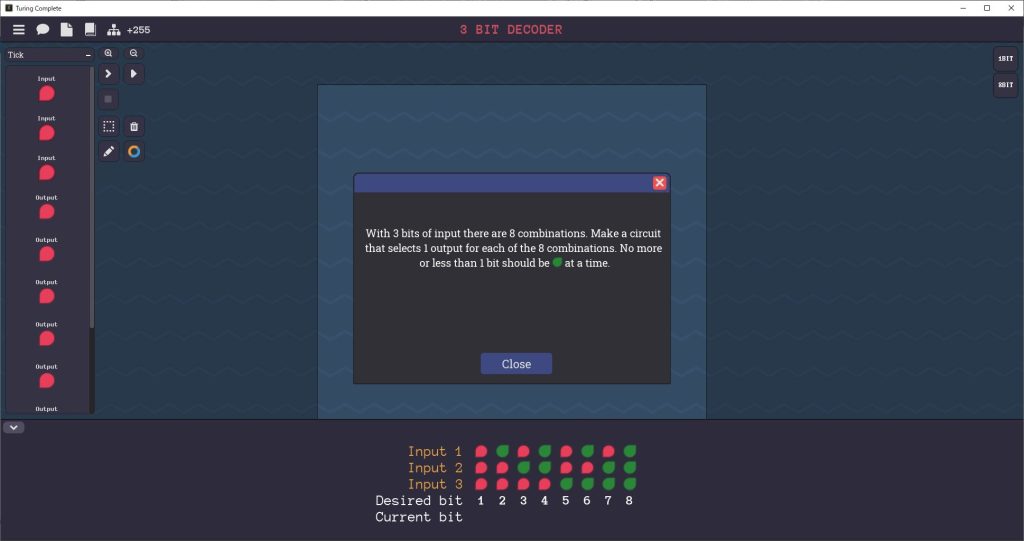

3ビットの入力だと、8つのパターンが存在します。

各パターンの入力が与えられたときに、8ビットある出力のうち別の桁に対応するような回路を組む問題です。

3 Bit Decoderステージを解く

2ビットデコーダーから自然に拡張する

2ビットデコーダーから3ビットデコーダーを作成してみます。

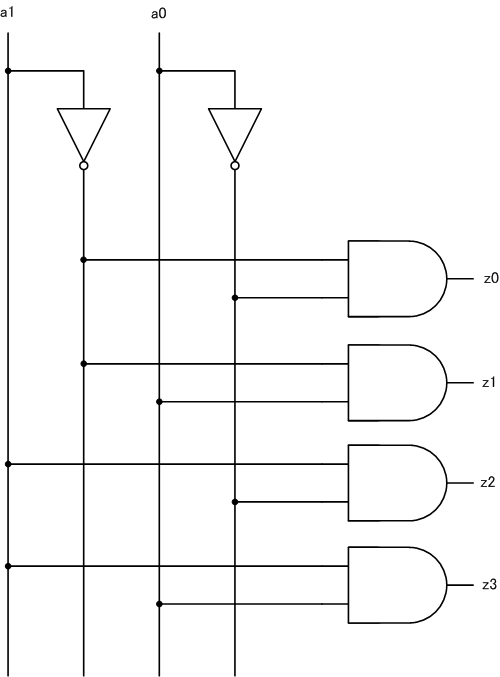

1:2ビットデコーダーの回路図を参照してください。いろいろなパターンがありますが、ここでは次の回路図を採用します。

※配線がわかりやすい回路図にしました。

挙動がわかりやすいようにコメントを追加すると次のようになります。

出力側には4つのANDゲートが並んでいますが、そのうち1つが1を出力すると、他のすべては0を出力します。

真理表は次の通りです。a0,a1が入力、z0~z3が出力です。

| a0 | a1 | z0 | z1 | z2 | z3 |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

これを見て、配線のパターンを理解してください。

方針としては、2ビットデコーダーを作ってから、3ビットデコーダーに拡張してみます。そうすれば、自然に3本目の入力線を考えられます。

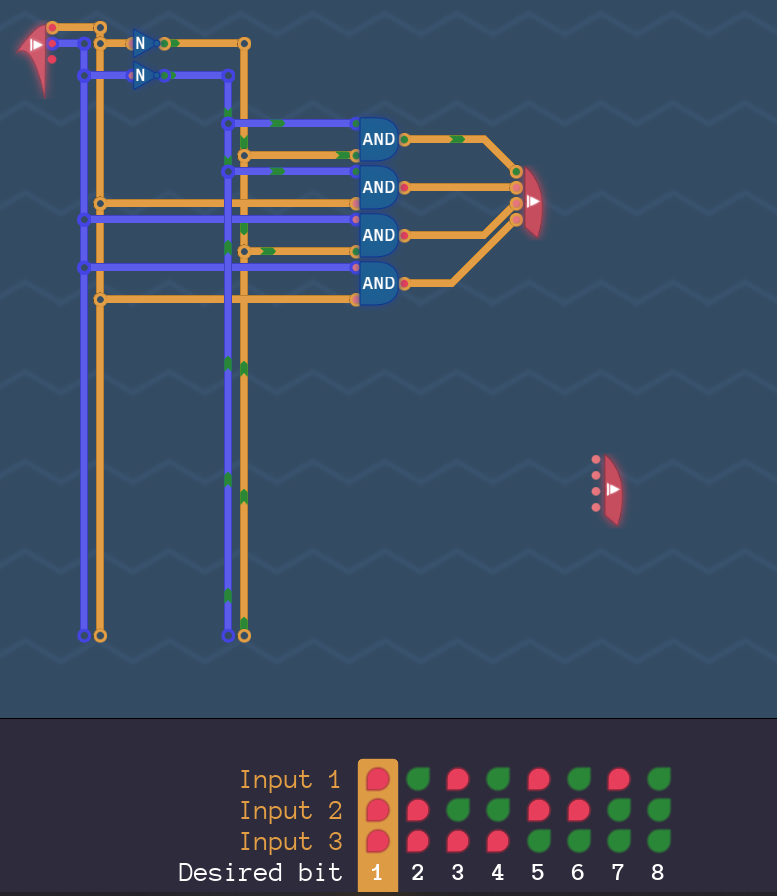

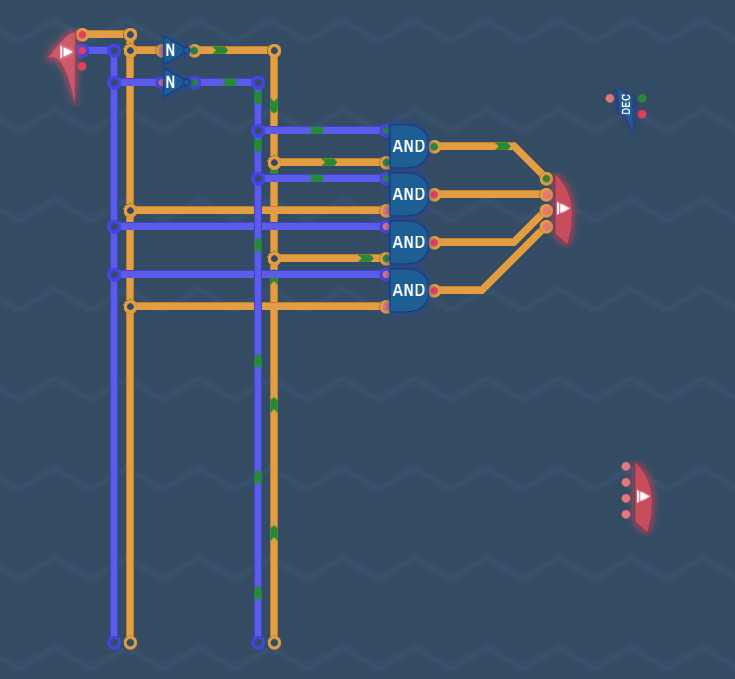

2:このステップでは、2ビットデコーダーの作成を目指します。

2つ目の出力モジュールは使わないので、離しておきます。

出力が4本なので、ANDゲート(ここではまだ2入力タイプ)を4つ並べます。入力が2本なので、NOTゲートが2つ並べます。配線をして、2ビットデコーダーが完成させます。

真理表の半分だけを見て、一致していることを確かめておきます。

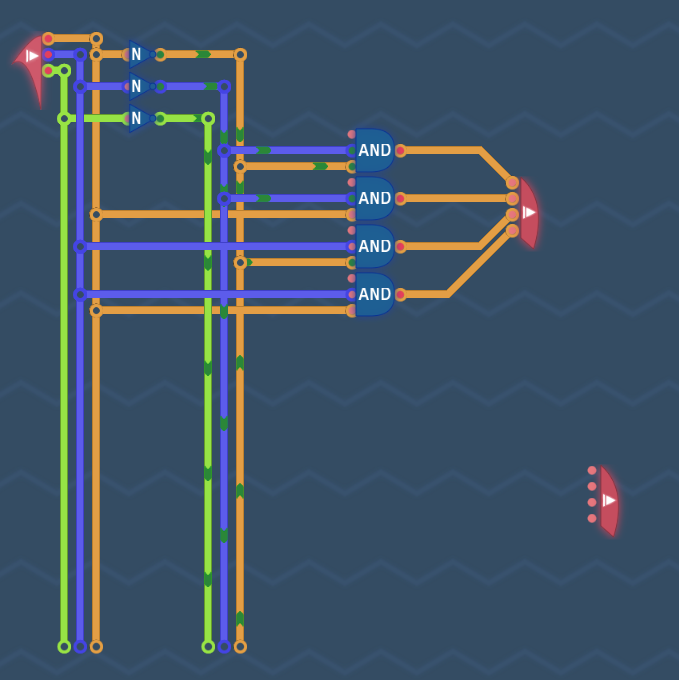

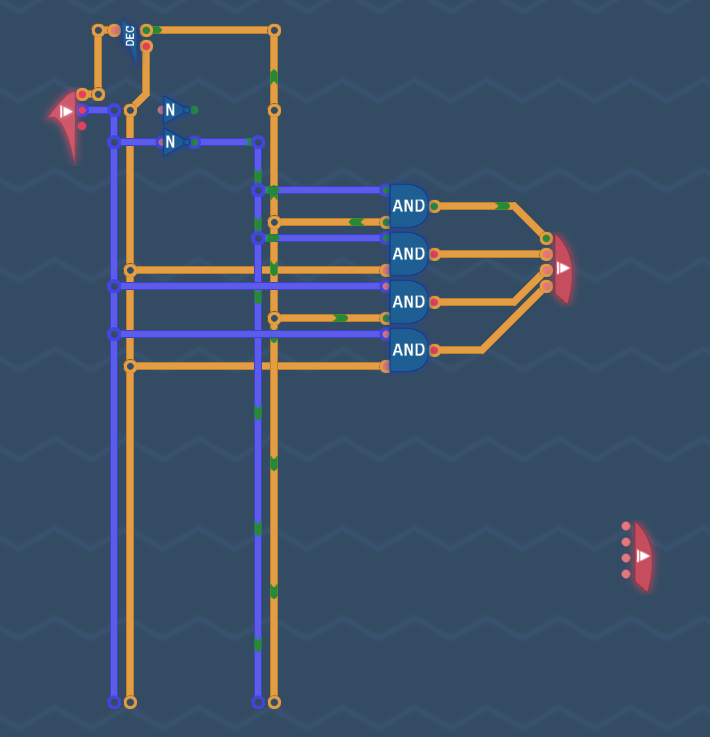

3:3ビットデコーダーに拡張する準備をしましょう。

ANDゲートを3入力タイプに置き換えます。

そして、配線も修正します。ANDゲートなので入力の並びは任意ですが、ここでは青線をずらしました。これで、ANDゲートの入力は上から、3ビットデコーダーの上位桁に対応します。

ここで、真理値表を再確認して、配線ミスがないことを確認しておきます。

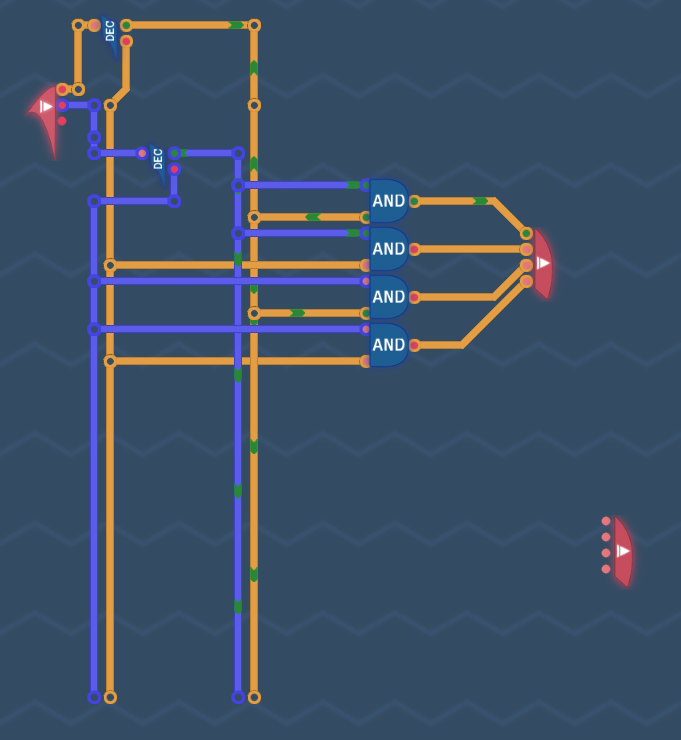

4:ここからは3ビットデコーダーを作っていきます。

入力付近にNOTゲートを1つ追加します。このNOTゲート前後の配線をします。

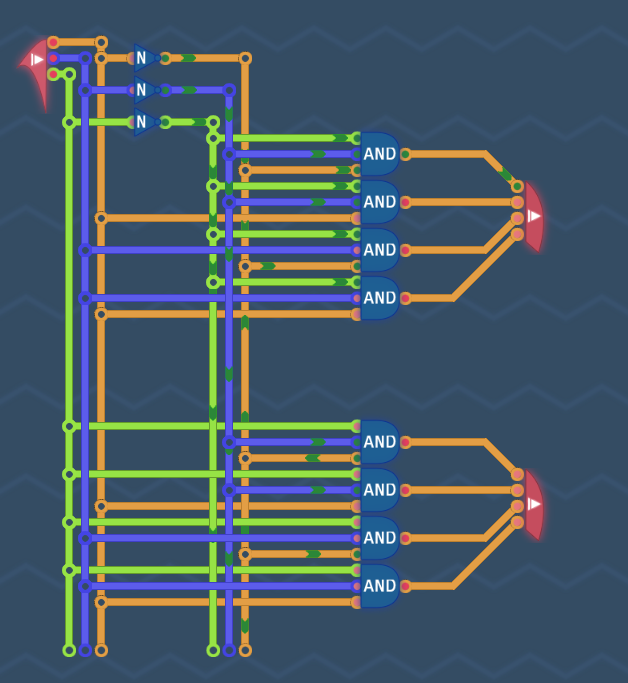

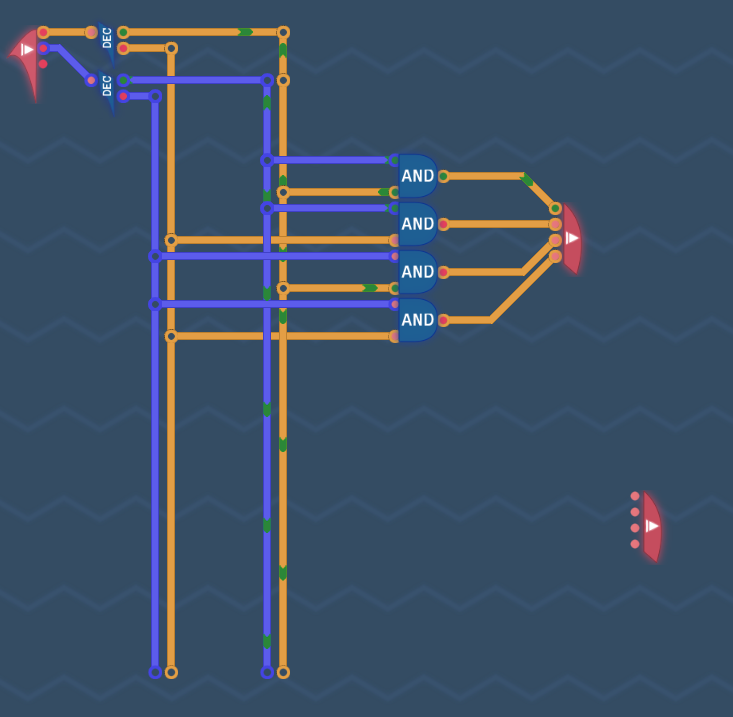

5:2つ目の出力モジュールを並べて、3入力タイプのANDゲートを同様に並べます。その際、範囲選択して、配線ごとコピー&ペーストすると効率的であり、配線ミスもなくなります。

6:後は緑線をANDゲートの入力につなげるだけです。これまでと同様な配線の並びでつないでみてください。

最後に真理表を見て、全パターンを確認します。

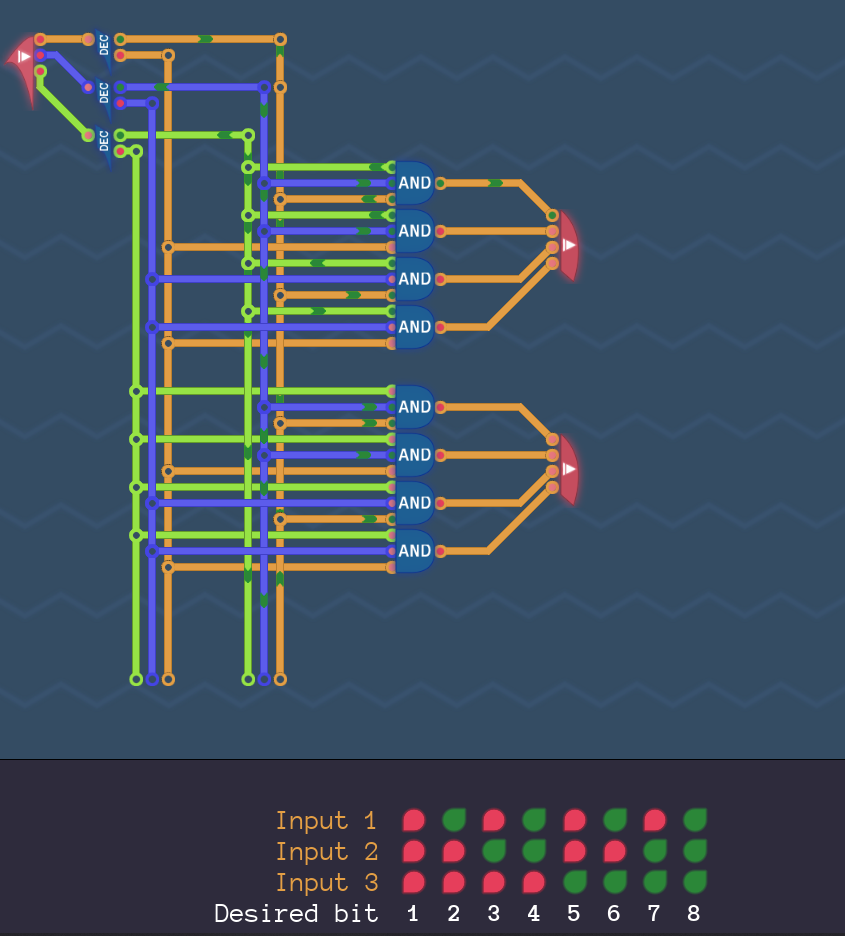

7:問題なさそうなら、テストしてみます。

1ビットデコーダーのモジュールを活用する

すでに1 Bit decoderコンポーネントとして使用可能な状態になっています。

1 Bit decoderコンポーネントを活用して、3ビットデコーダーを作ってみます。

1:次の回路は2ビットデコーダーを基本的な論理ゲートが完成したところ(先のステップ2で得られた)です。

この回路内で1ビットデコーダーに置き換えてみます[1]この1ビットデコーダーは上がNOTゲートありの配線です。)。

まずは橙線だけに注目すればよいでしょう。

1本ずつ線をつなげたら、元の回路の線を1本ずつカットするとわかりやすいです。DECゲートの入出力の線がすべて接続され、NOTゲートの入出力の線がすべて切断されたら一応の完成になります。

真理表を頭でトレースとして問題なければ、NOTゲートを削除します。

2:同様にして青線でも2つ目のDECゲートを使うようにします。

3:配線がぐちゃぐちゃなのできれいにします。

これで2ビットデコーダーが完成しました。

4:3ビットデコーダーに拡張します。

2入力タイプのANDゲートを3入力タイプに置き換えます。ANDゲートへの入力の配線を若干調整します。

後は範囲選択でコピー&ペースとして、2つ目の出力モジュールに配線します。

3番目の入力にDECゲートを追加して、同様の配線をします。

※流れは、先の回路設計と同様です。

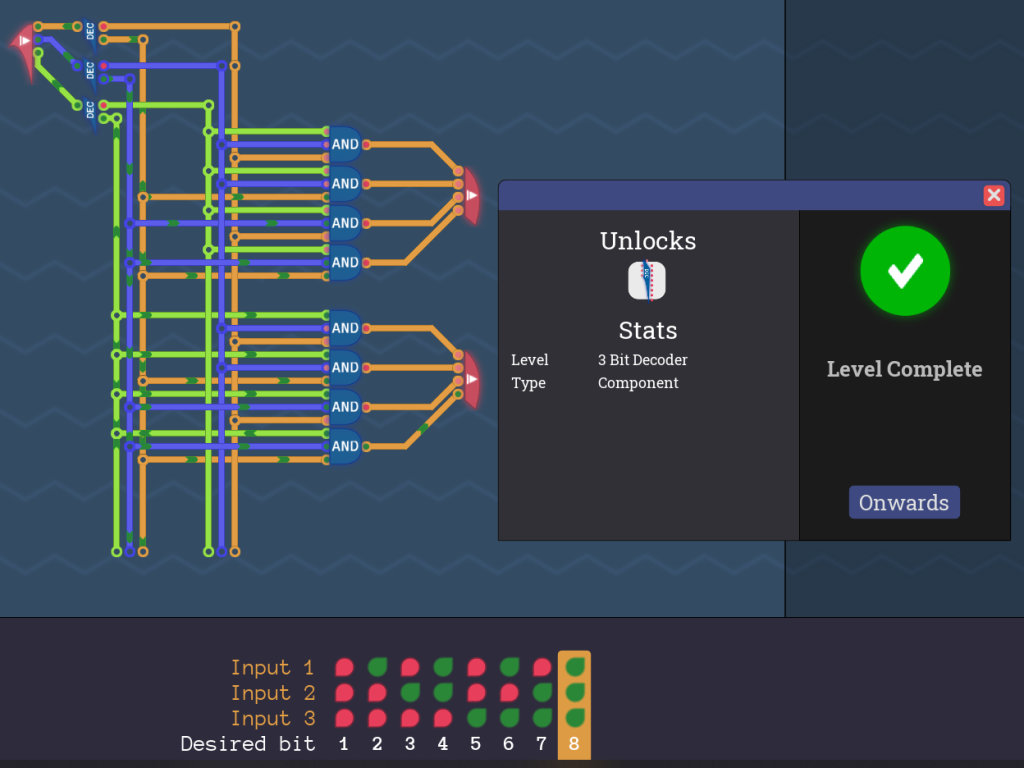

完成したらテストしてください。

クリアすると、3 Bit decoderコンポーネントがアンロックします。

アドレスデコーダーに応用する

RAM内のメモリセルマトリクスの行・列を指定するのにデコーダーが使えます。

例えば、16行16列のメモリセルマトリクスがあった場合、4ビットデコーダーが2つ[2]行レコーダーと列レコーダーの2つになります。あれば、アクセスするセルが確定できます。

データインを持つ3線-8線デコーダーに拡張する

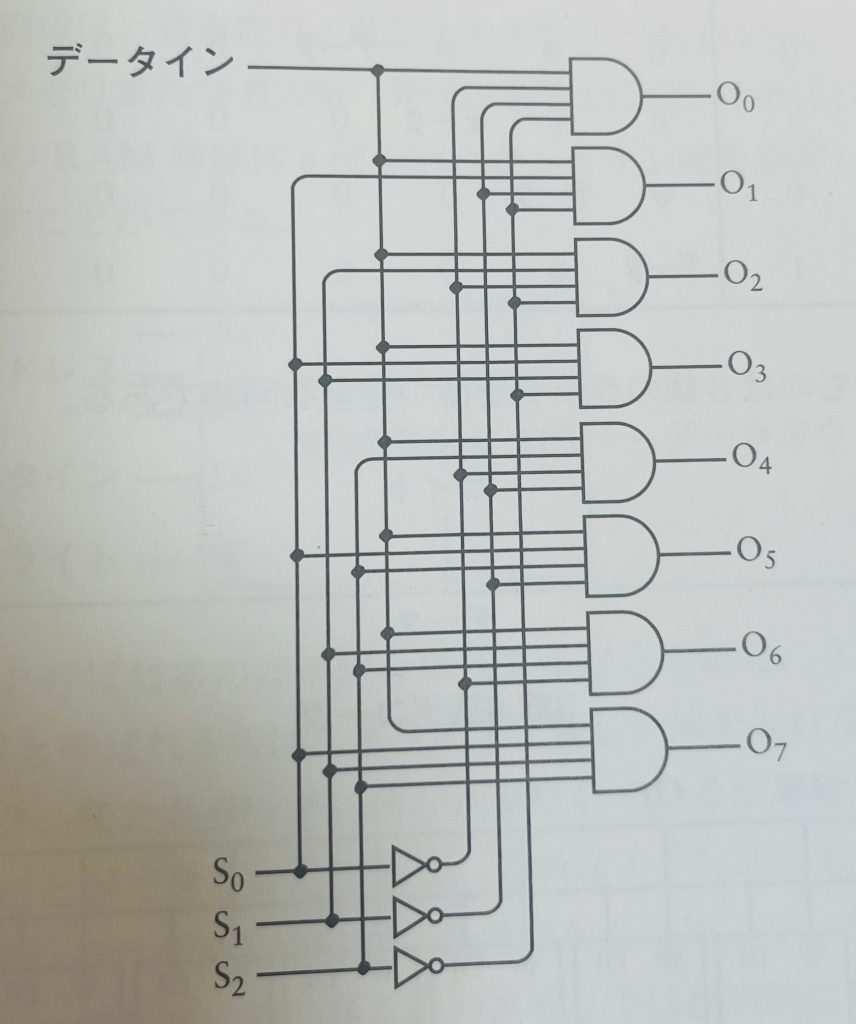

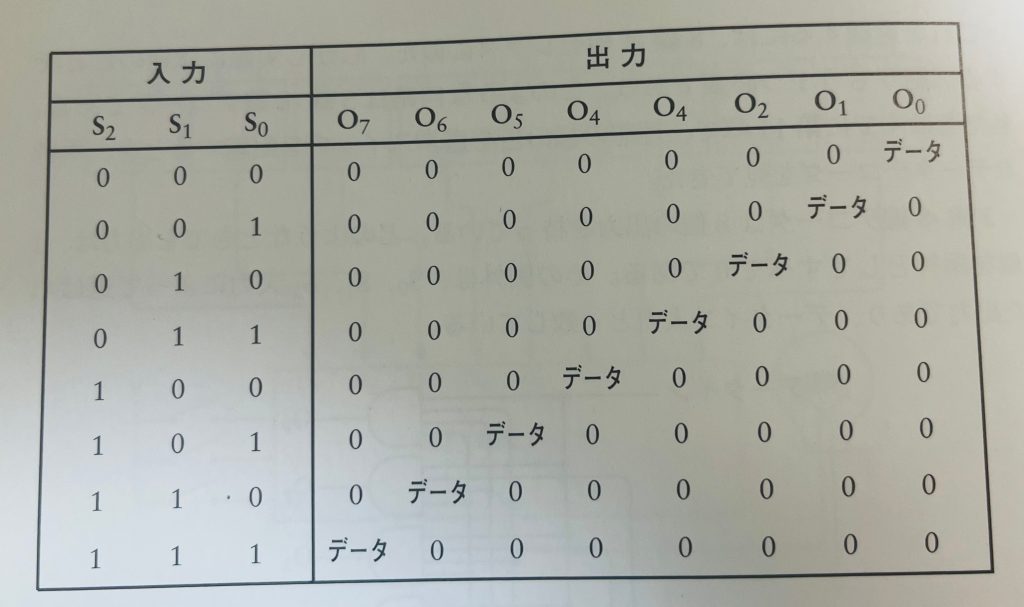

『CODE』P.249ではデータインを持つ3線-8線デコーダーが登場します。

これは3ビットデコーダーに入力としてデータインが1本追加されたものになります。真理表を見るとわかりますが、デコード結果の出力位置がTになるわけではなく、データインのT/Fが反映されます。

この3線-8線デコーダーを用いて、8個のラッチを持つ完全な回路を構成できます。どのラッチを使うかを確定するために利用されています。

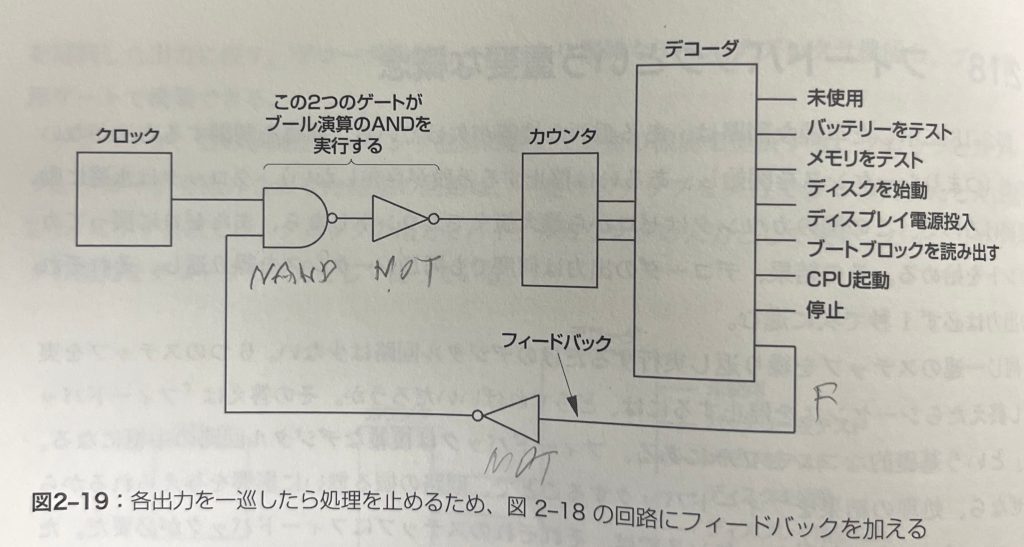

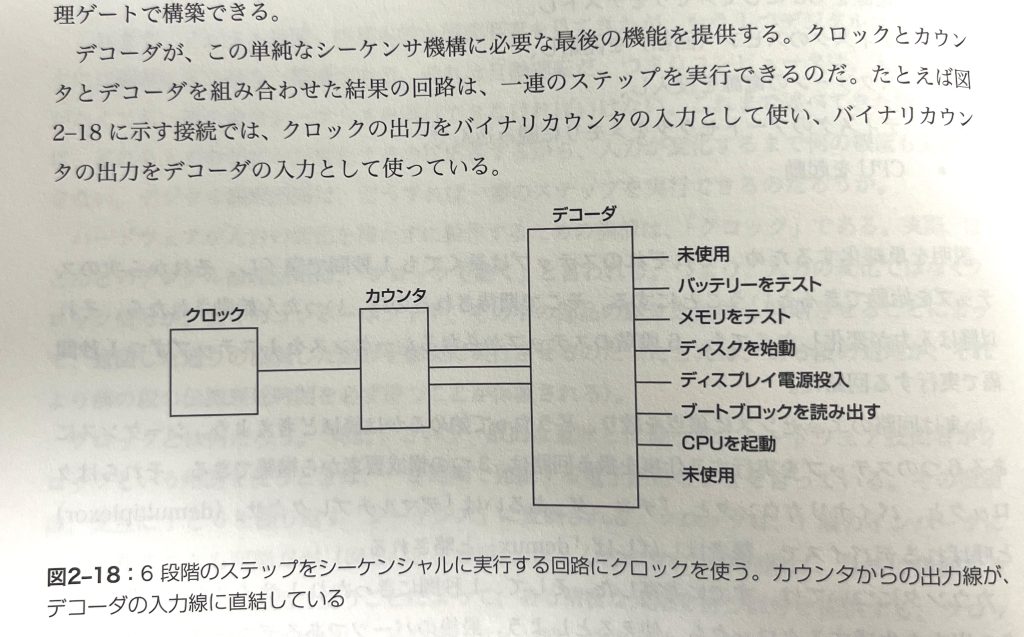

デコーダーで単純なシーケンサー機構を実現する

クロック+カウンター+デコーダーにより、一連のステップを実行できます。

一連(6つ)の操作を終えたらシーケンスを止めるには、(カウンターの入力側に)フィードバックさせればよいことになります。

次の回路では、CLOCK and (not F)がカウンターの入力になります。F=0のときだけ、カウンターの入力が続くのを許します。