Transistor level【NandGame編】

目次

はじめに

いつもブログをご覧いただきありがとうございます。

ミジンコに転生したIPUSIRONです😀

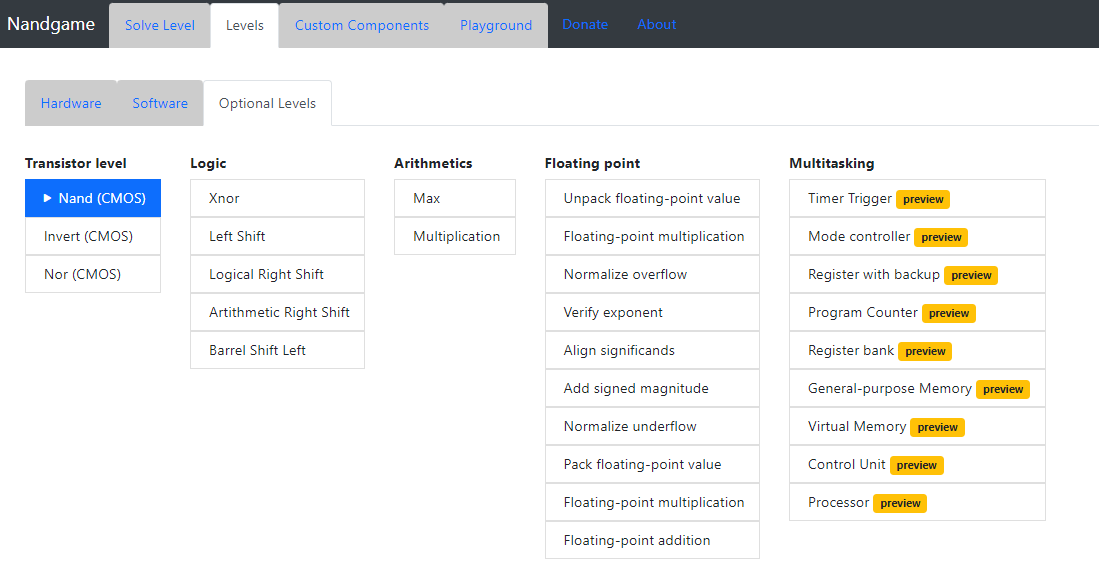

Transistor level

ここからOptional Levelsに入ります。

すでにNand、Invert、Norの回路を実装しましたが、ここではCMOS型のトランジスターを利用して回路を実装します。

トランジスターのスイッチング作用

以下の記事はMOSFET型のトランジスターですが、スイッチング作用については基本的に同様の考え方になります。

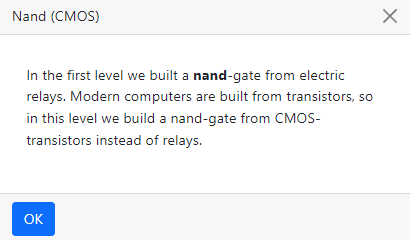

Nand (CMOS)レベル

Nand (CMOS)レベルのゴールは、COMS型トランジスターを使ってNANDゲート(CMOS NANDゲート)を組むことです。

※リレーを使ったNANDゲートについては、HardwareのNandレベルで解きました。

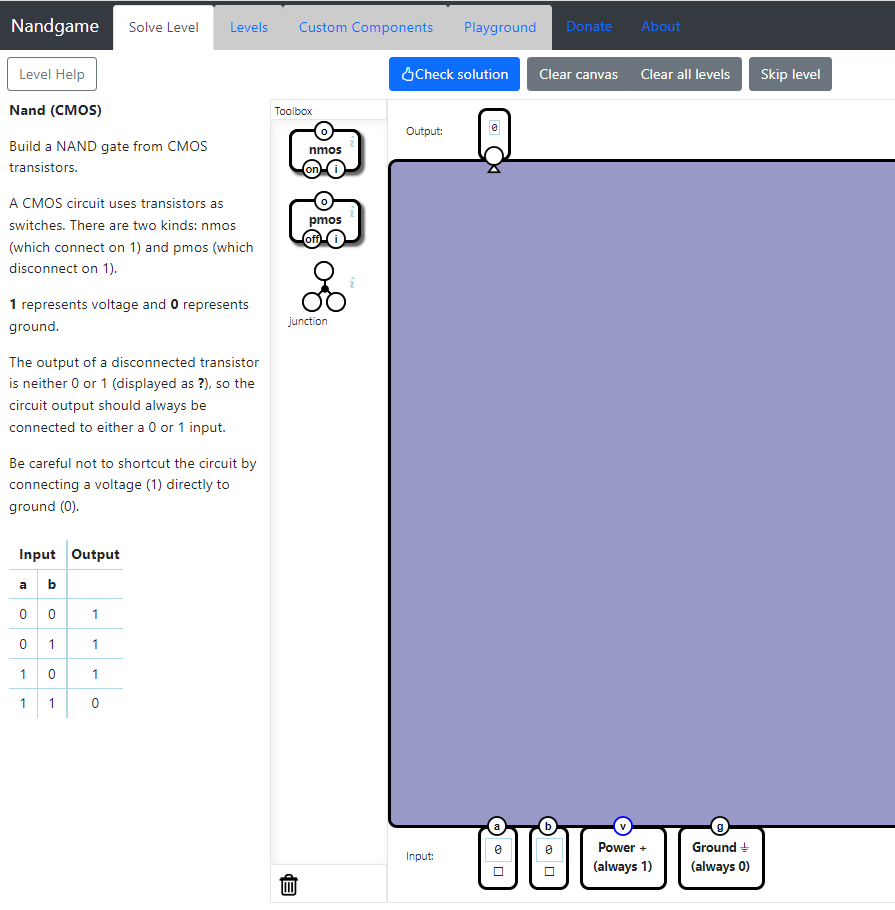

NandGameで使えるコンポーネント

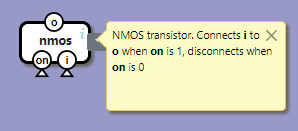

nmos

nMOSトランジスターに相当するコンポーネントです。

入力端子はonとi、出力端子はoになります。

NandGameでは電子的なスイッチとして活用するので、onによって、iとoの接続状態を制御するとイメージすれば十分です。

[1]onが1のとき⇒iとo間が接続

[2]onが0のとき⇒iとo間が接続断

※左側の入力端子が"on"となっているのでH(1)のときに、スイッチが入って、i(=input)端子とo(=output)端子間のワイヤーが内部的につながると覚えましょう。

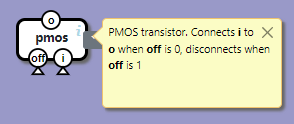

pmos

pMOSトランジスターに相当するコンポーネントです。

入力端子はoffとi、出力端子はoになります。

[1]offが1のとき⇒iとo間が接続

[2]offが0のとき⇒iとo間が接続断

junction

ワイヤーの連結点です。

NandGameの仕様上、各コンポーネントの出力を直接接続できません。このjunctionコンポーネントを使うことで間接的に接続できます。

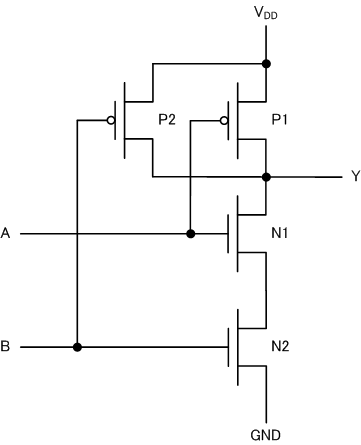

(2入力の)CMOS NANDゲートの回路

pMOSトランジスターP1とP2は並列に接続されています。

一方のpMOSトランジスターがONなら、出力YはVDDに引き上げられます。

プルアップ回路網とプルダウン回路網に抽象化するとわかりやすいです。

pMOSプルアップ回路網の内部では、pMOSトランジスターが並列に接続されています。対して、nMOSプルダウン回路網の内部では、nMOSトランジスターが直列に接続されています。

上図の右をCMOS NOTゲートの回路図と見比べてください。すると、回路網を一種の電子的なスイッチと見れば、「pMOSプルアップ回路網がSW=ON」かつ「nMOSプルアップ回路網がSW=OFF」であれば、出力は1になります。

今回のCMOS NANDゲートの回路図によると、pMOSプルアップ回路網にpMOSトランジスターが並列に並んでいました。つまり、これらのトランジスターの1つでもONなら、pMOSプルアップ回路網はSW=1になります。

nMOSプルダウン回路網にはnMOSトランジスターが直列に並んでいます。すべてのトランジスターがONなら、nMOSプルダウン回路網はSW=1になります。

以上を真理値表にまとめると次が得られます。

| A | B | プルアップ回路網 | プルダウン回路網 | 出力Y |

|---|---|---|---|---|

| 0 | 0 | ON | OFF | 1 |

| 0 | 1 | ON | OFF | 1 |

| 1 | 0 | ON | OFF | 1 |

| 1 | 1 | OFF | ON | 0 |

※太字のところが出力Yが1になる条件です。

プルアップ回路網とプルダウン回路網はお互いON・OFFが違っています。

・プルアップ回路網とプルダウン回路網の両方が同時にONになると、VDDとGNDが短絡してショートする。

・両方がOFFだと、出力端子はVDDとGNDのどちらにも接続していない状態(Z∞)になる。

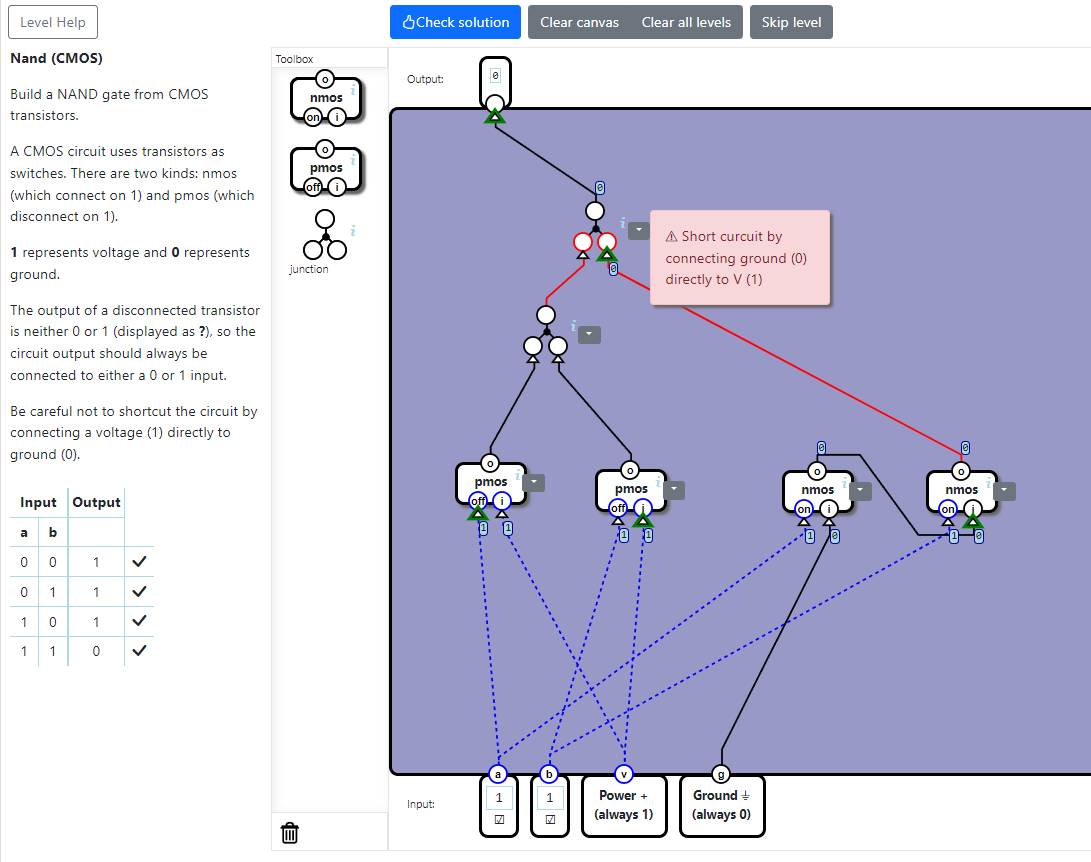

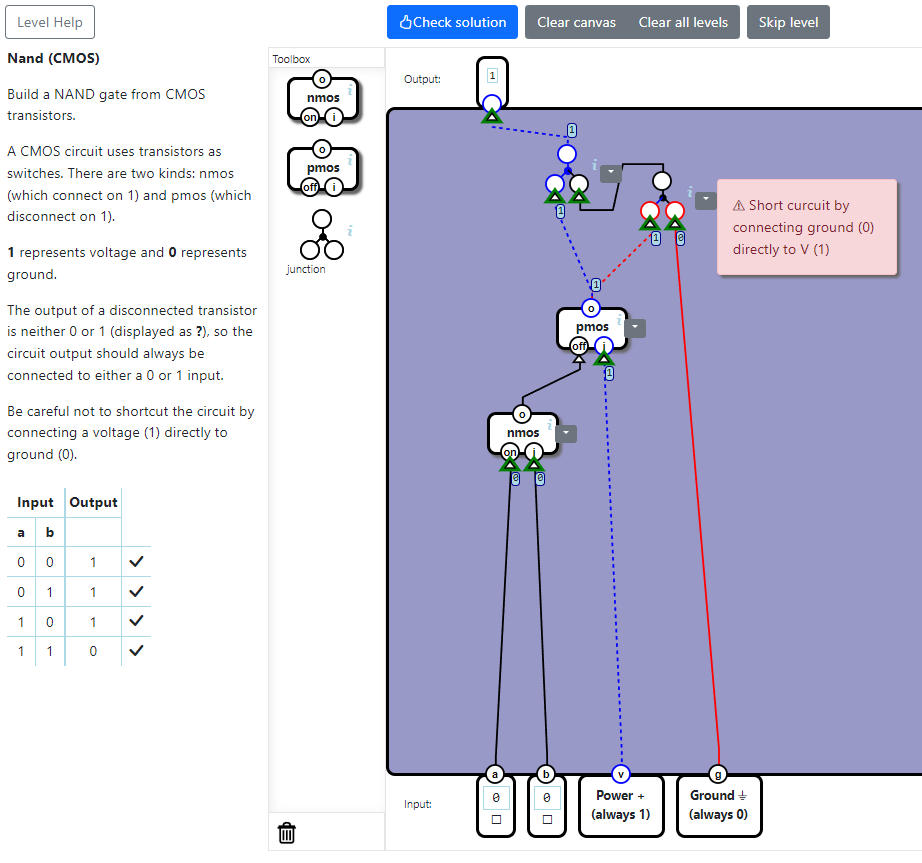

Nand (CMOS)レベルを解く

よく見かける回路は、4個のCMOS(2個のpMOS、2個のnMOS)を使って構成されています。

これをNandGameで実装すると次のようになります。

よく見かける回路はショートしませんが、ここで示した回路ではショートしています。ところが、当該レベルについてはクリアとなります。

執筆時点(2023年12月)、この辺りの仕様について微妙なので、将来的に修正される可能性があります。

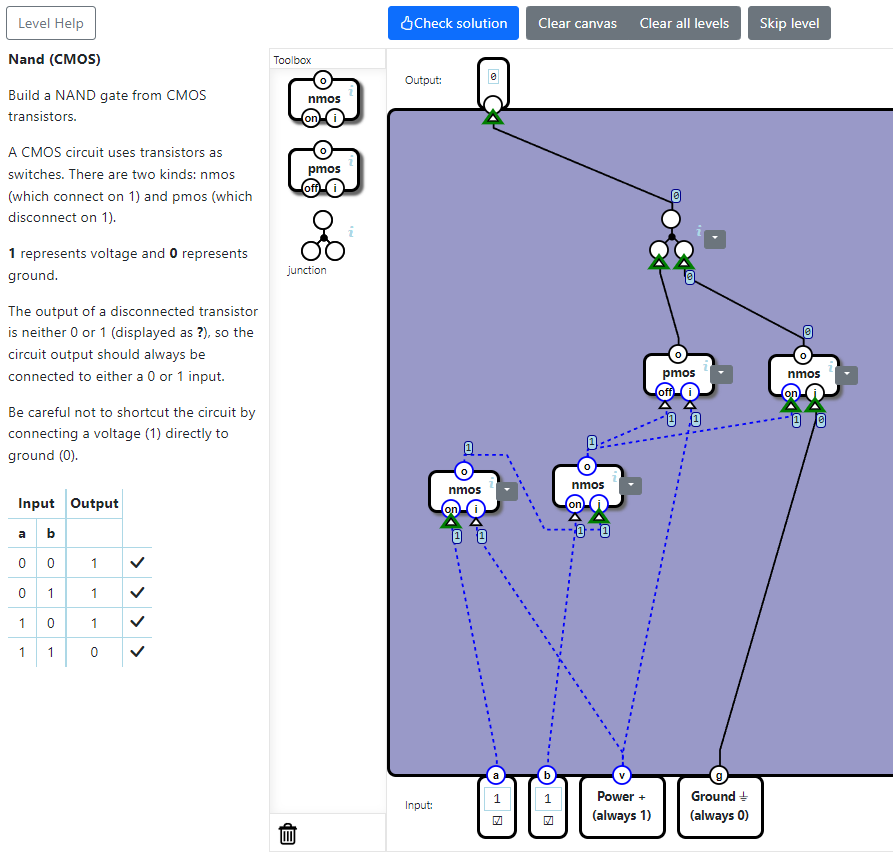

junctionを無理矢理利用したバージョン【別解】

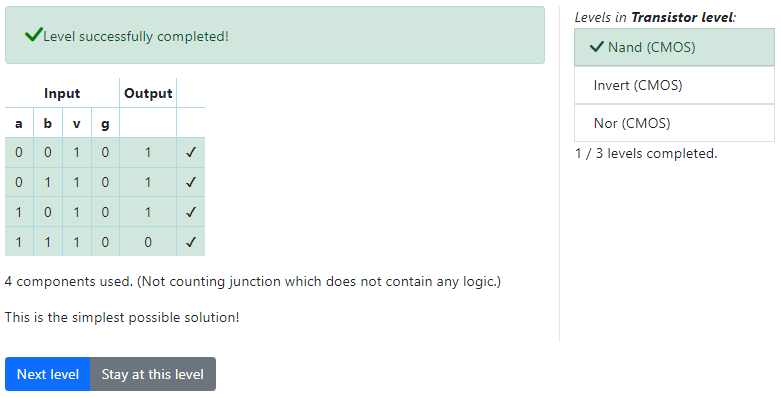

NandGame用に最適化したCMOS NANDゲートの回路【別解2】

3個のnmos、1個のpmosを使います。この回路だとショートのワーニングは表示されません。

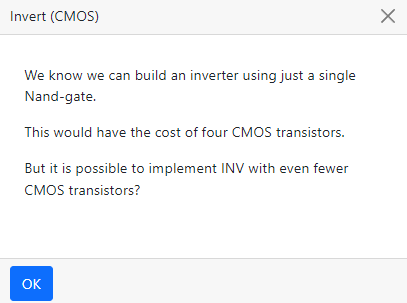

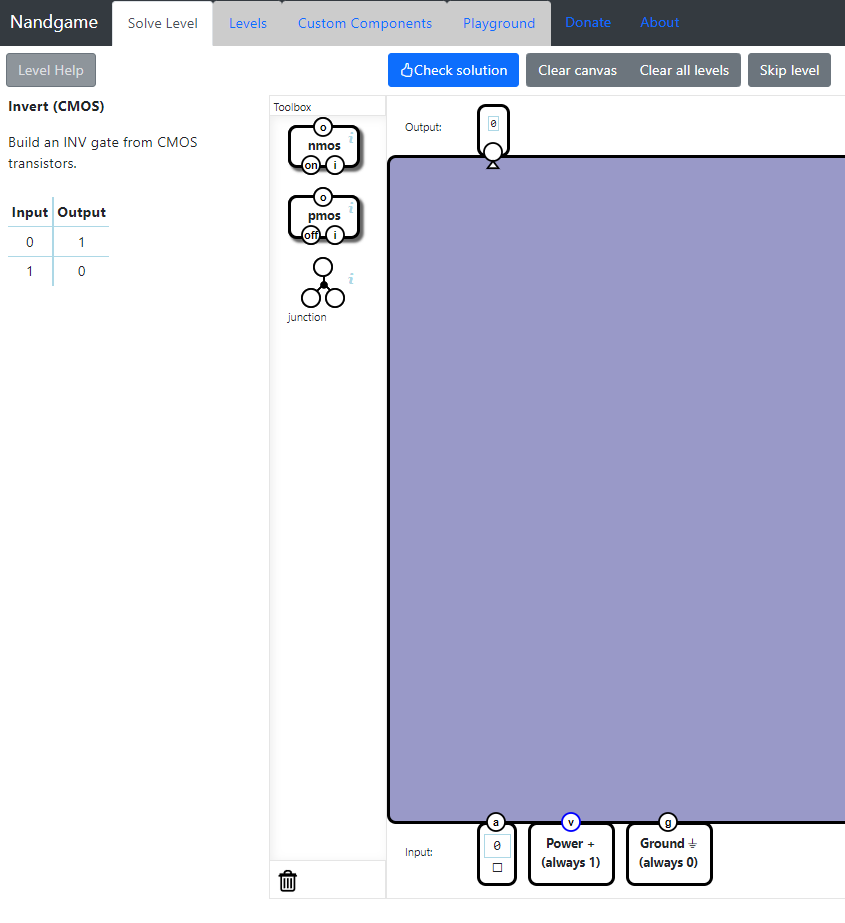

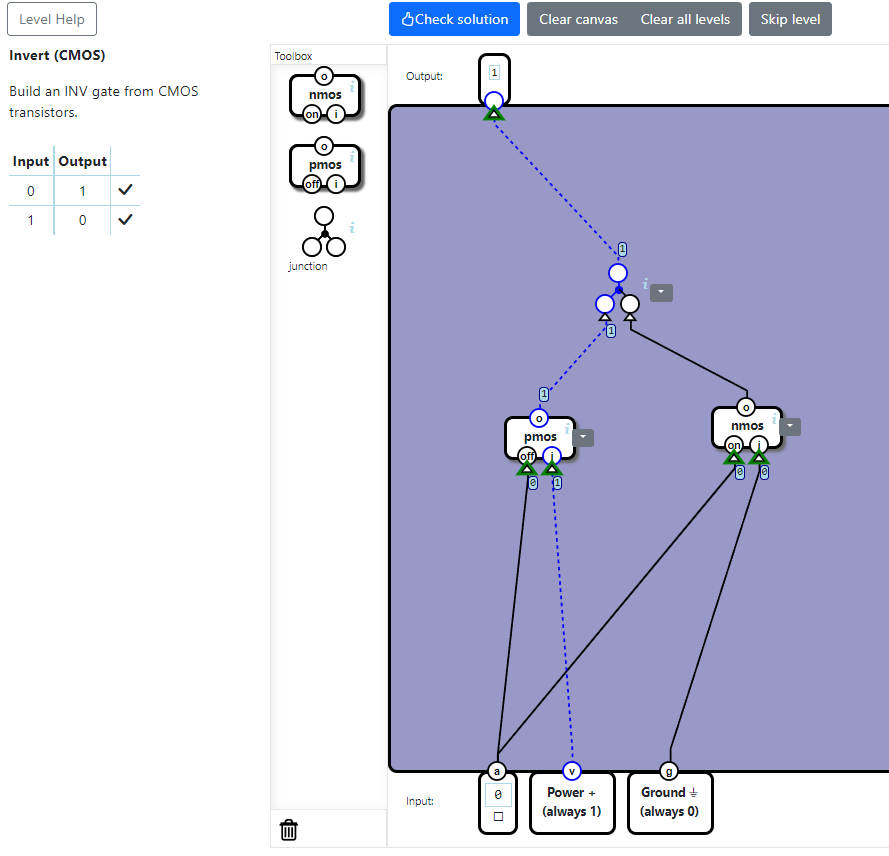

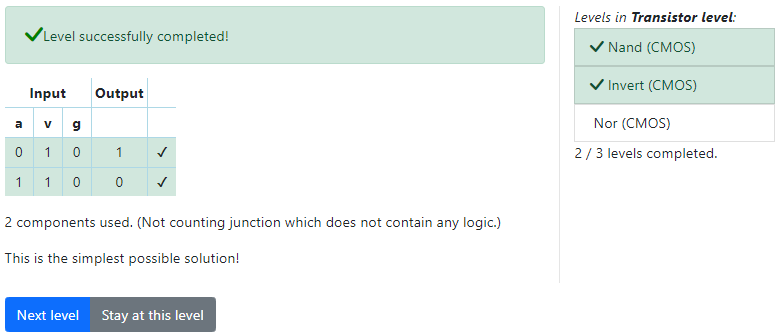

Invert (CMOS)レベル

Invert (CMOS)レベルのゴールは、COMS型トランジスターを使ってNOTゲート(CMOS NOTゲート)を組むことです。

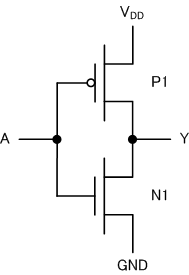

CMOS NOTゲートの回路

nMOSトランジスターN1は、GNDと出力Yの間に存在します。対して、pMOSトランジスターP1は、VDDと出力Yの間に存在します。両方のトランジスターN1とP1のゲートは、入力Aによって制御されます。

[1]A=0のとき

⇒「N1はOFF」かつ「P1はON」

⇒YはVDDと接続され、GNDと接続されていない。

⇒出力Yは論理レベルの1に引き上げられる。

※pMOSトランジスター(P1)は1を出力するのが得意であり、それをうまく活用しています。

[2]A=1のとき

⇒「N1はON」かつ「P1はOFF」

⇒YはGNDと接続され、VDDと接続されていない。

⇒出力Yは論理レベルの0に引き下げられる。

※nMOSトランジスター(N1)は0を出力するのが得意であり、それをうまく活用しています。

Invert (CMOS)レベルを解く

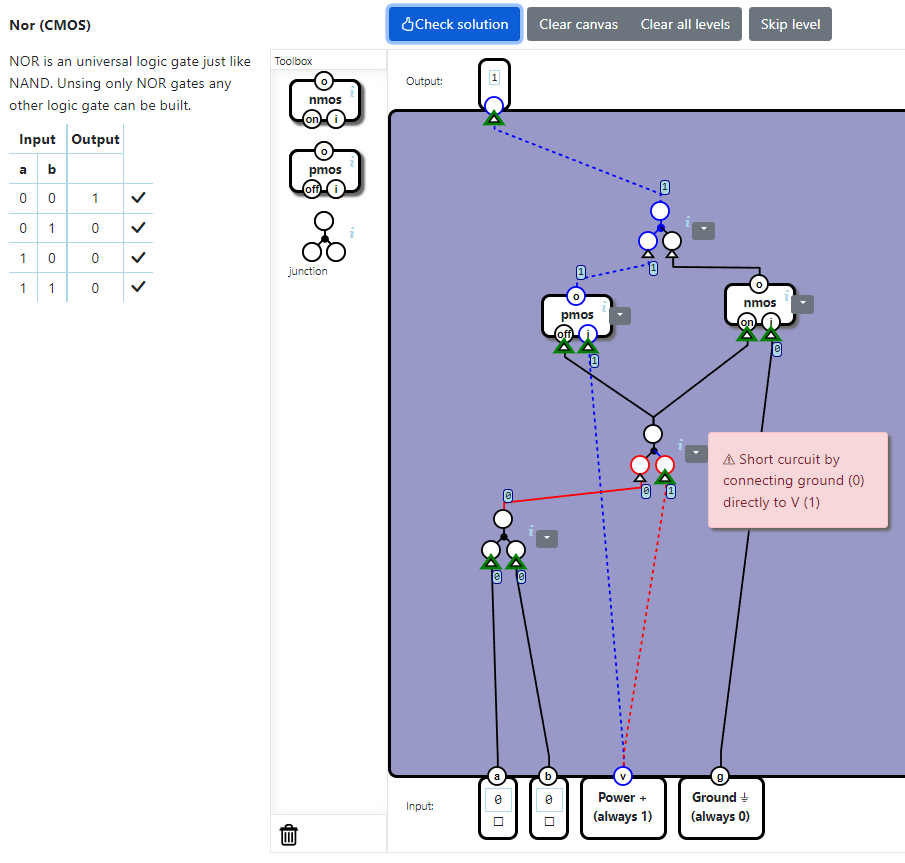

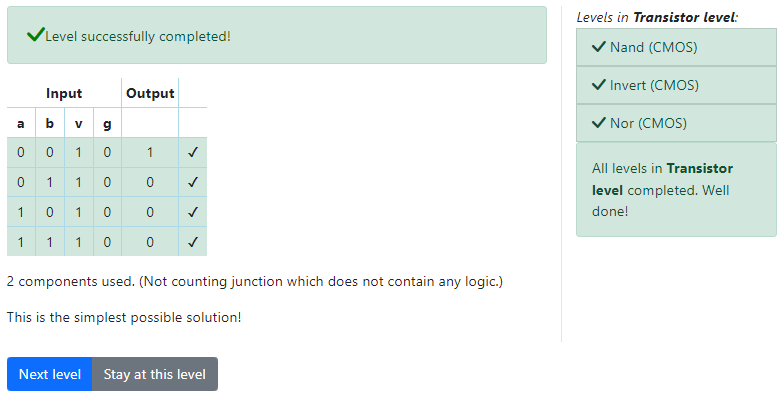

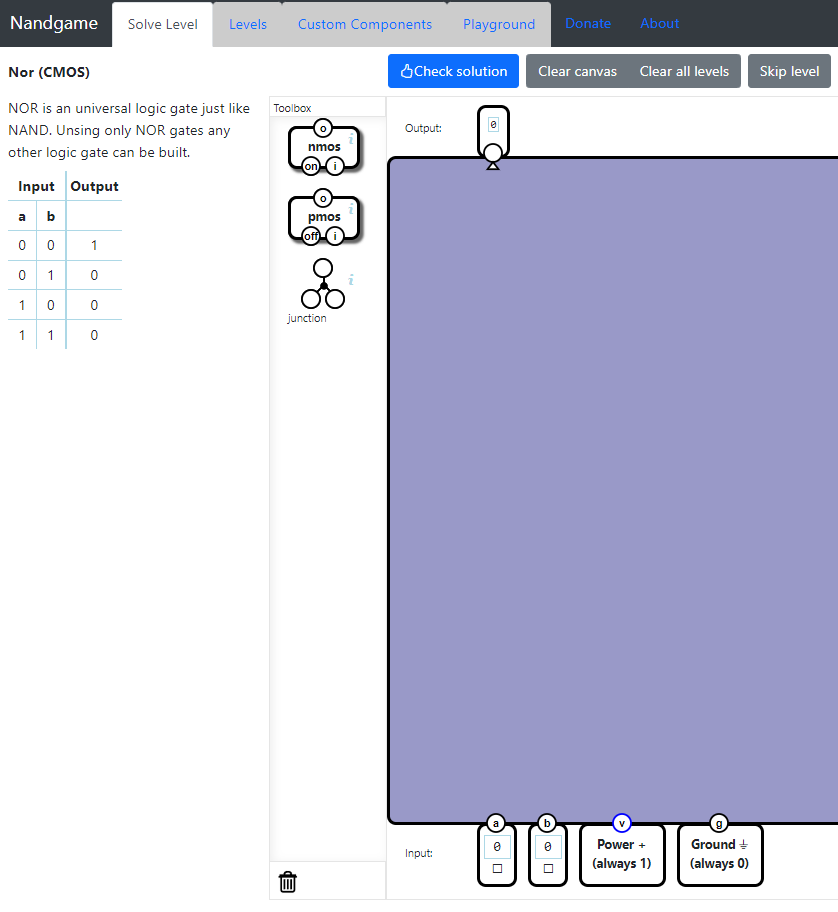

Nor (CMOS)レベル

Nor (CMOS)レベルのゴールは、COMS型トランジスターを使ってNORゲート(CMOS NORゲート)を組むことです。

Nor (CMOS)レベルを解く