Alter ego (NMOS)【Hard Chip編】

はじめに

いつもブログをご覧いただきありがとうございます。

ミジンコに転生したIPUSIRONです😀

Alter ego (NMOS)ステージ

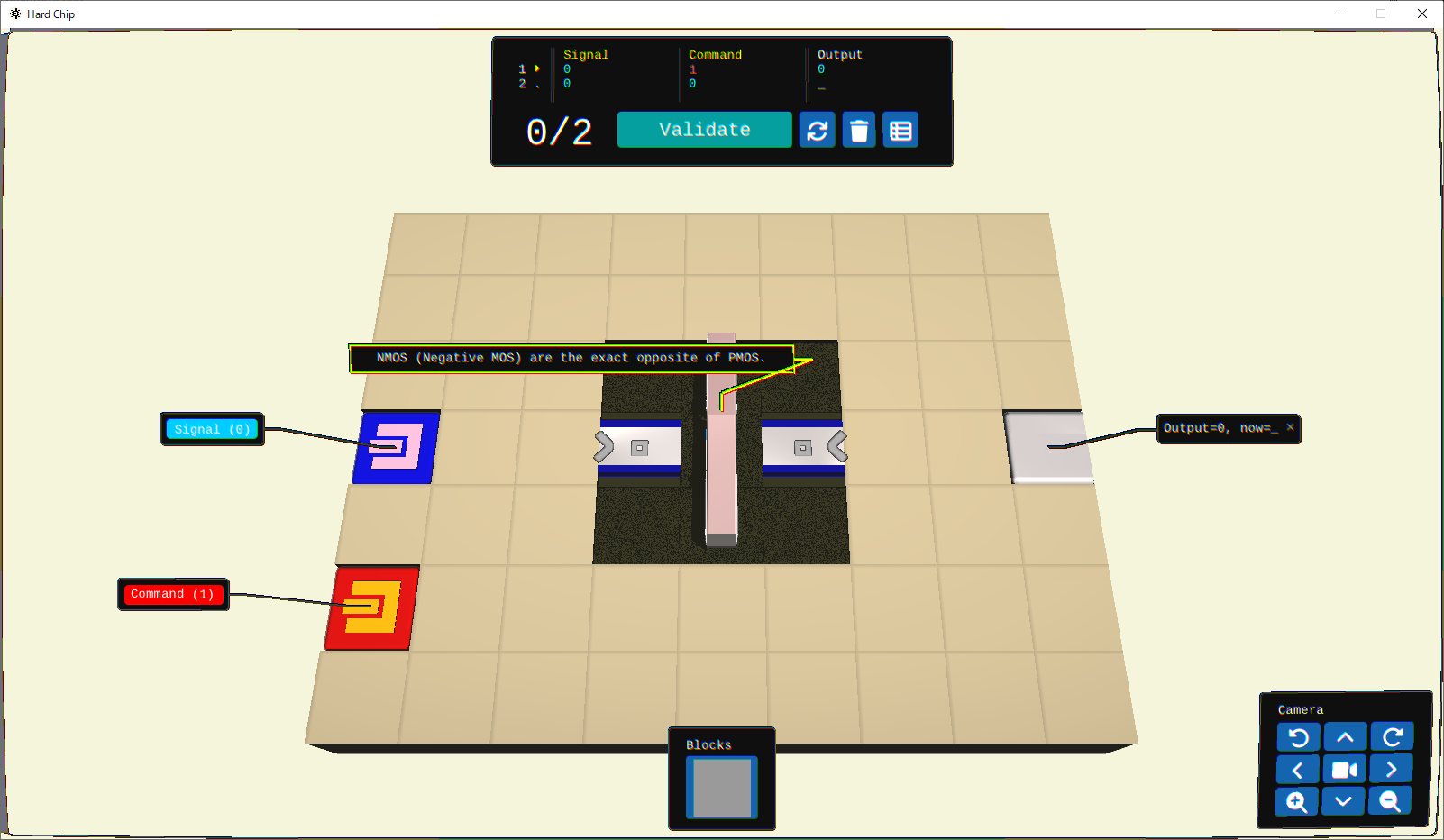

Alter ego (NMOS)ステージは、Transistorsセクションの2番目のステージです。

2入力1出力の回路であり、NMOS回路(nMOSトランジスターに相当)を利用して、導通を制御する回路を組むのがゴールになります。

Alter ego (NMOS)ステージを解く

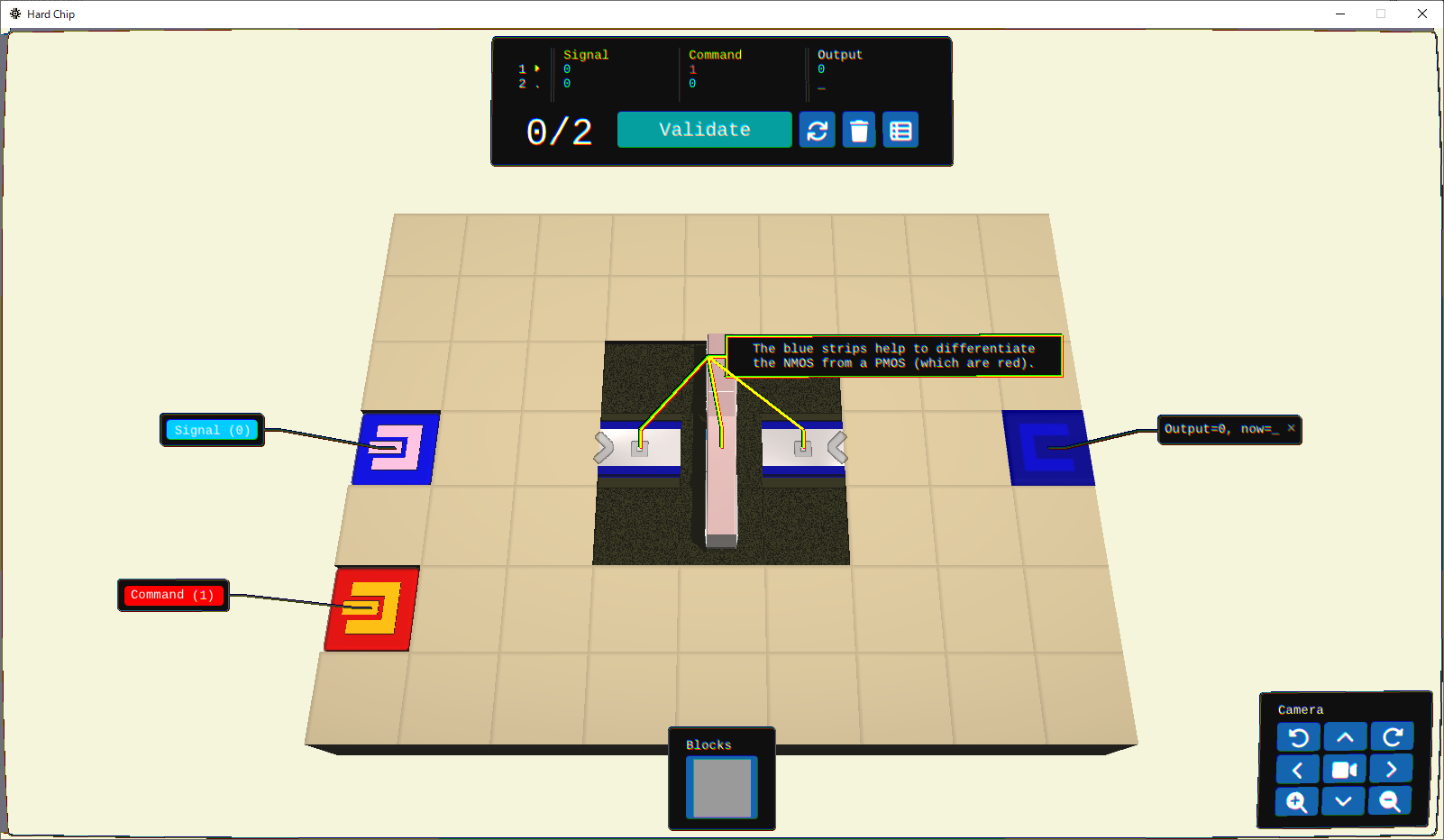

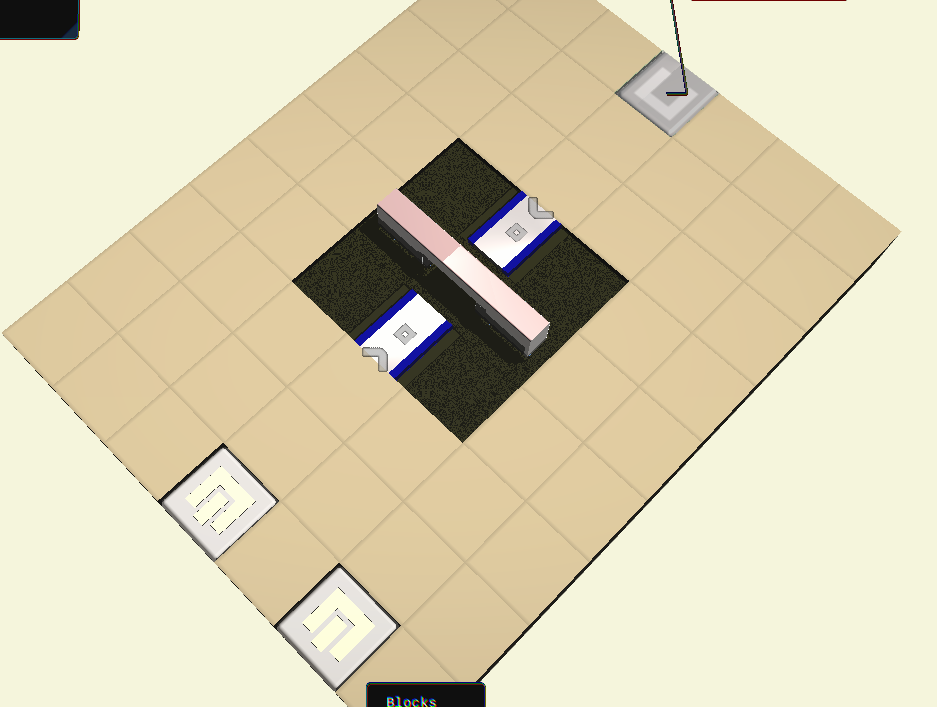

1:初期回路を見る

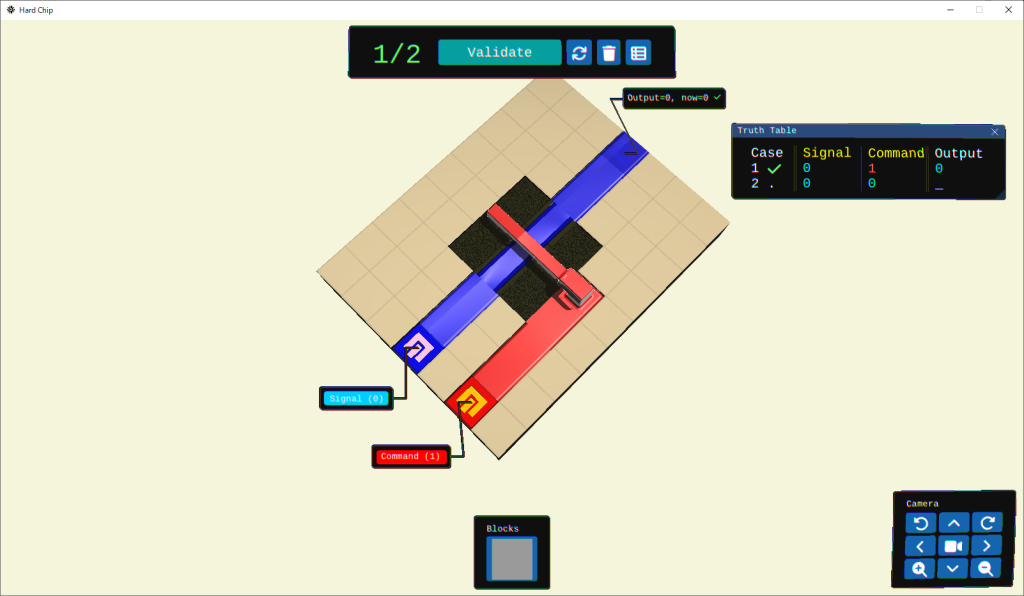

2入力、1出力であることがわかります。

中央にある回路は、Two To One (PMOS)ステージに登場した回路と似ていますが、Channelの色が青の違いがあります。

青は0を意味しているため、0かオープンを制御する回路であることが推測できます。

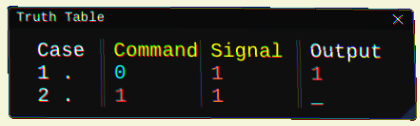

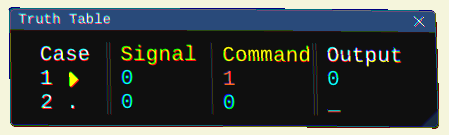

2:真理値表を確認する

Two To One (PMOS)ステージとAlter ego (NMOS)ステージの真理値表を比較してみます。

CommandとSignalの列が逆転しているのに注意してください。

・PMOSの場合は、出力は1かなしです。Commandが0のときにSignalをそのまま通して、1を出力します。

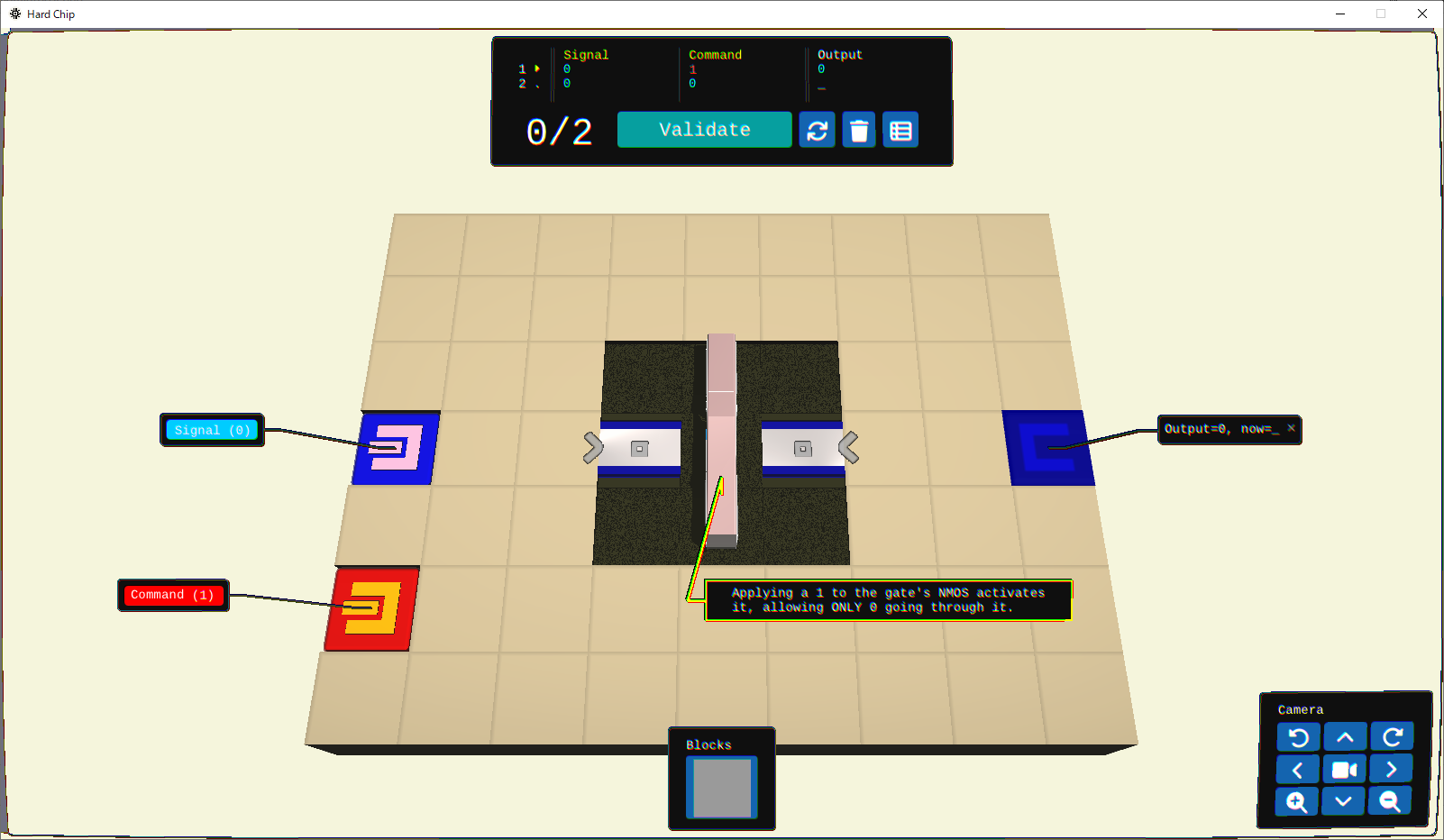

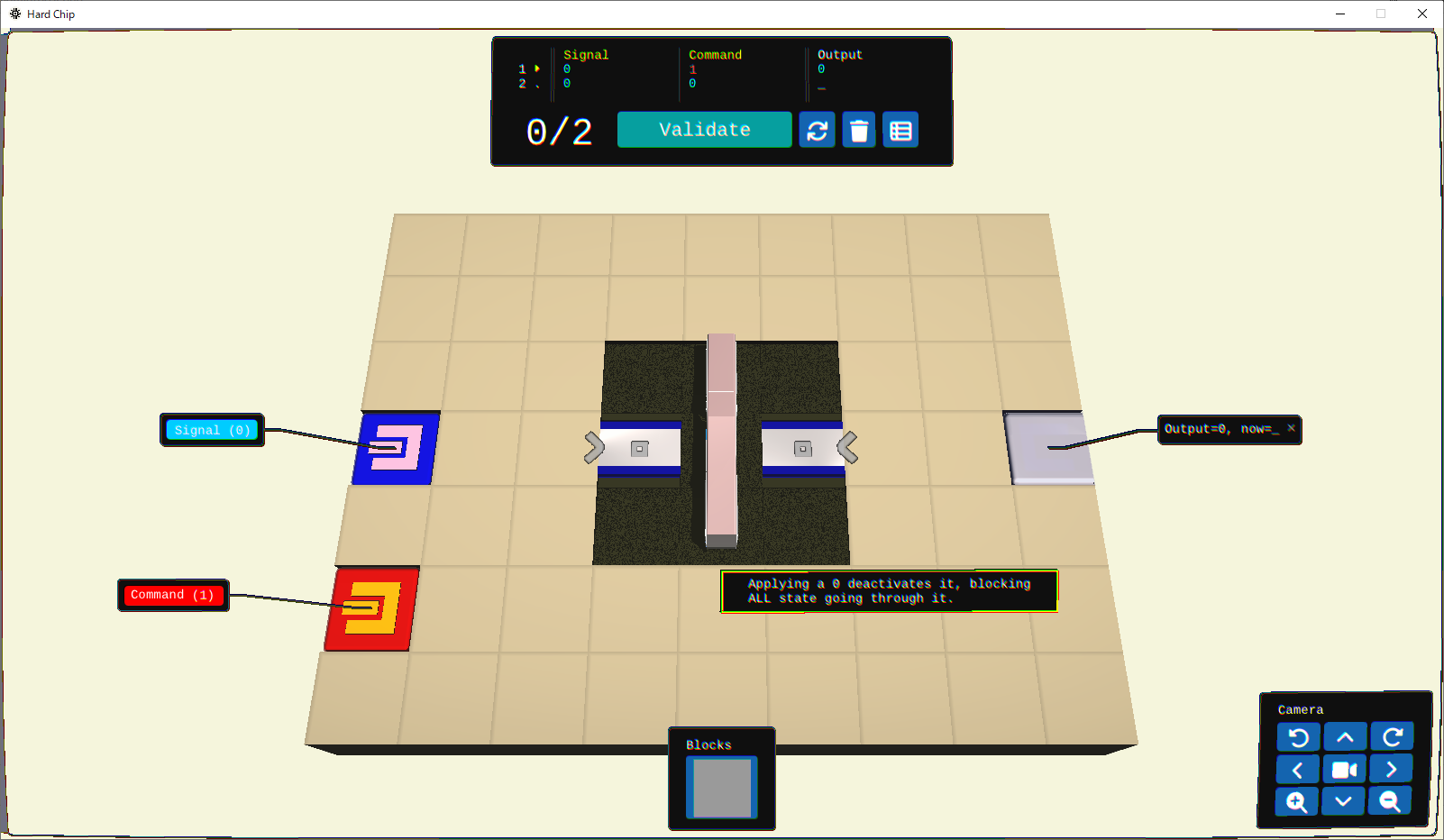

・NMOSの場合は、出力が0かなしです。Commandが1のときにSignalをそのまま通して、0を出力します。

NMOSの挙動については次の記事も参考にしてください。

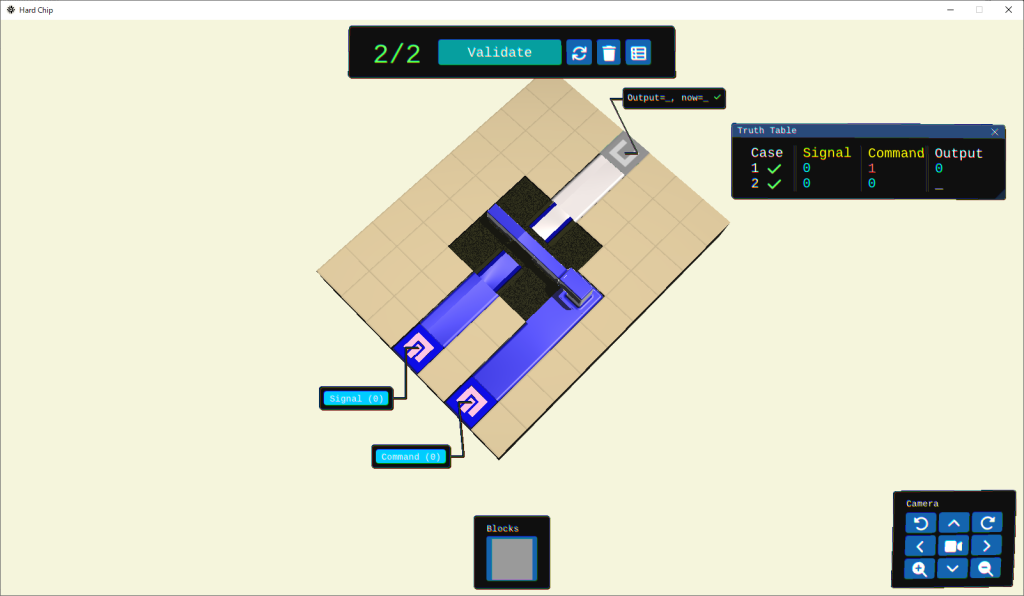

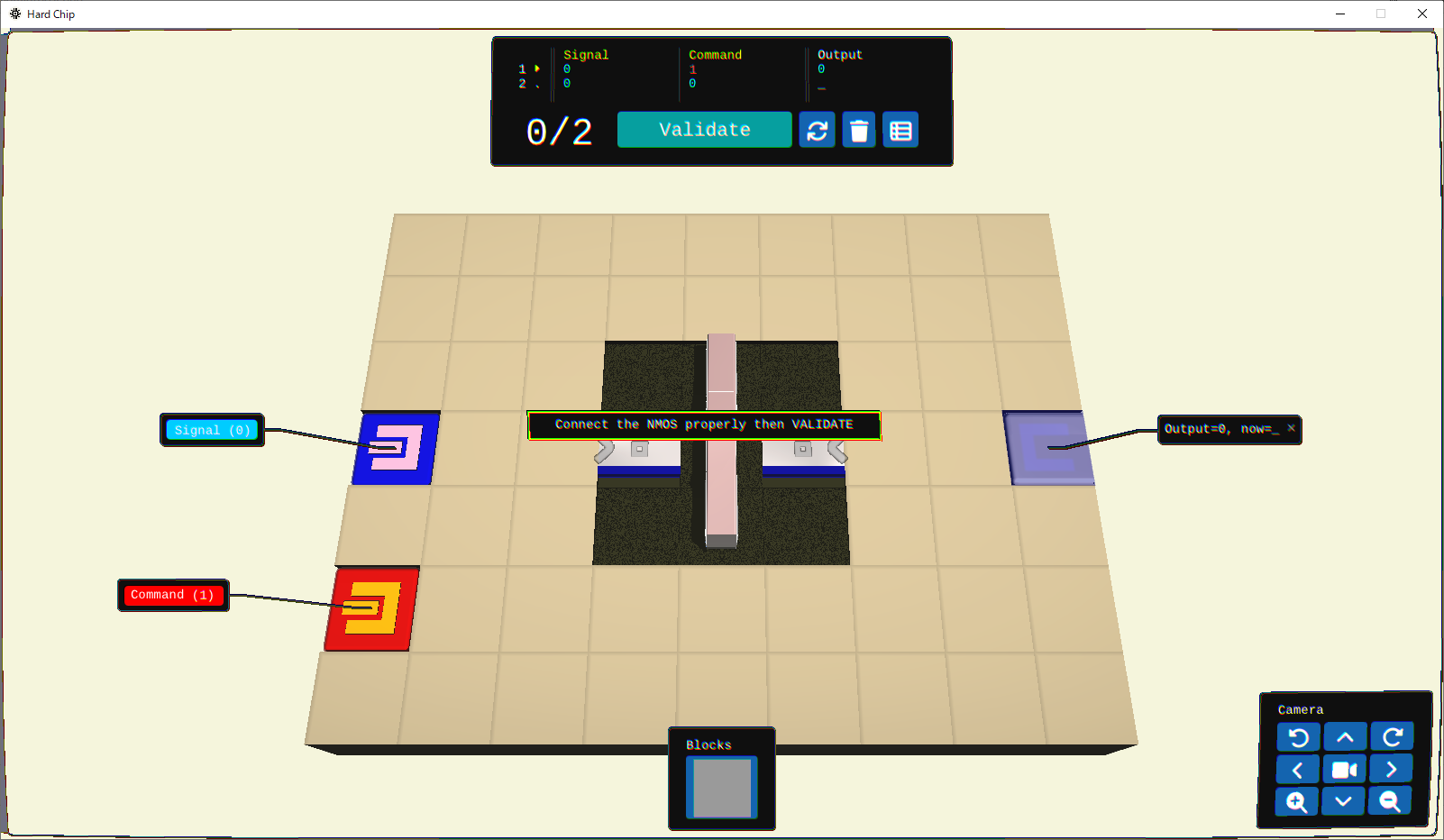

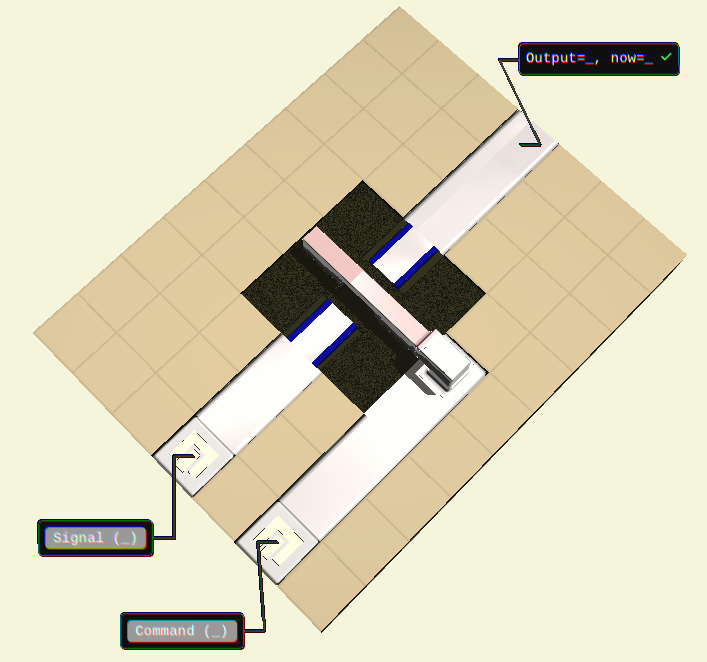

3:回路を組む

入力Signalと出力Outputの通過・遮断を制御する回路なので、ここは一本道です。中央のNMOS回路の下(Channel)を通ります。

消去法的に入力Commandは、NMOS回路の上(Gate)に接続することになります。

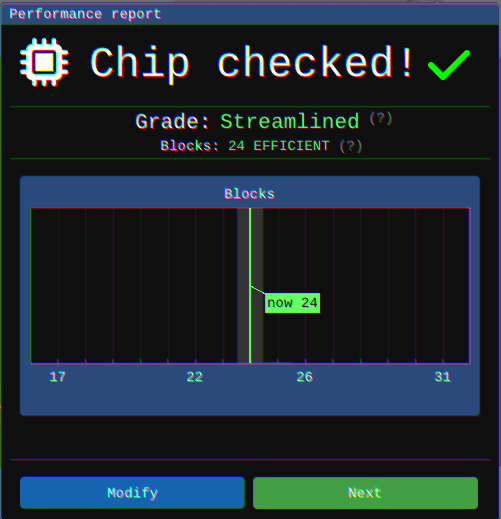

4:回路を検証する

真理値表の2パターンが成立して、クリアになります。