Latch【NandGame編】

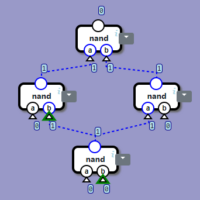

Latchレベルのゴールは、1ビットラッチを組むことです。

ラッチはビットを記憶し、出力します。つまり、1ビットラッチは1ビットを記憶したり出力したりできます。

入力にはdとstがあります。st ...

Register【NandGame編】

Registerレベルのゴールは、2つのD-FFを用いて、2ビットを記憶するレジスター回路を組むことです。

Registerレベルを解く

dffコンポーネント1つで1ビット分を記憶できます

Combined Memory【NandGame編】

Combined Memoryレベルのゴールは、複合メモリーを組むことです。

プロセッサーのメモリーは、AおよびDと呼ばれる2つの16ビットレジスターとRAMユニットで構成されます。

Control Unit【NandGame編】

プログラムは一連の命令から成り立ちます。そして、各命令はそれを決定するビットフラグの集まりであり、次の内容が確定します。

・実行するALU演算

・どのレジスターを入力として使用する ...

Instruction【NandGame編】

Instructionレベルのゴールは、ALU回路とCondition回路(条件判定回路)を内蔵した回路を組むことです。

※将来的に当該回路(Instruction回路と呼ぶことにする)は複合メ ...

Condition【NandGame編】

Conditionレベルのゴールは、条件判定回路を組むことです。

今回の条件判定は、ゼロと比べての大小比です。

組むべき回路の入出力は次のとおりです。

入力X:比較対象の16ビット ...ALU【NandGame編】

ALUレベルのゴールは、ALU(Arithmetic Logic Unit)回路を実装することです。

ALUレベルを解く

1:logic unitコンポーネントとarithmetic unitコンポ

Arithmetic Unit【NandGame編】

Arithmetic Unitレベルのゴールは、次の機能を持つ算術演算回路を実装することです。

入力・op0とop1:オペコードフラグ。2つで2ビット。・X:演算される側の16ビット ...

Logic Unit【NandGame編】

Logic Unitレベルのゴールは、次の機能を持つ論理演算回路を実装することです。

入力・op0とop1:オペコードフラグ。2つで2ビット。・X:演算対象の16ビット列

・Y:演算対 ...

「第100回 ゆるいハッキング大会」にて登壇しました

2023年10月21日に「第100回 ゆるいハッキング大会」にて登壇しました。

約1年ぶりに東京に行ったので浦島太郎状態でした。

「 ...