シグナルディレイの実装【The Signal State編】

はじめに

いつもブログをご覧いただきありがとうございます。

ミジンコに転生したIPUSIRONです😀

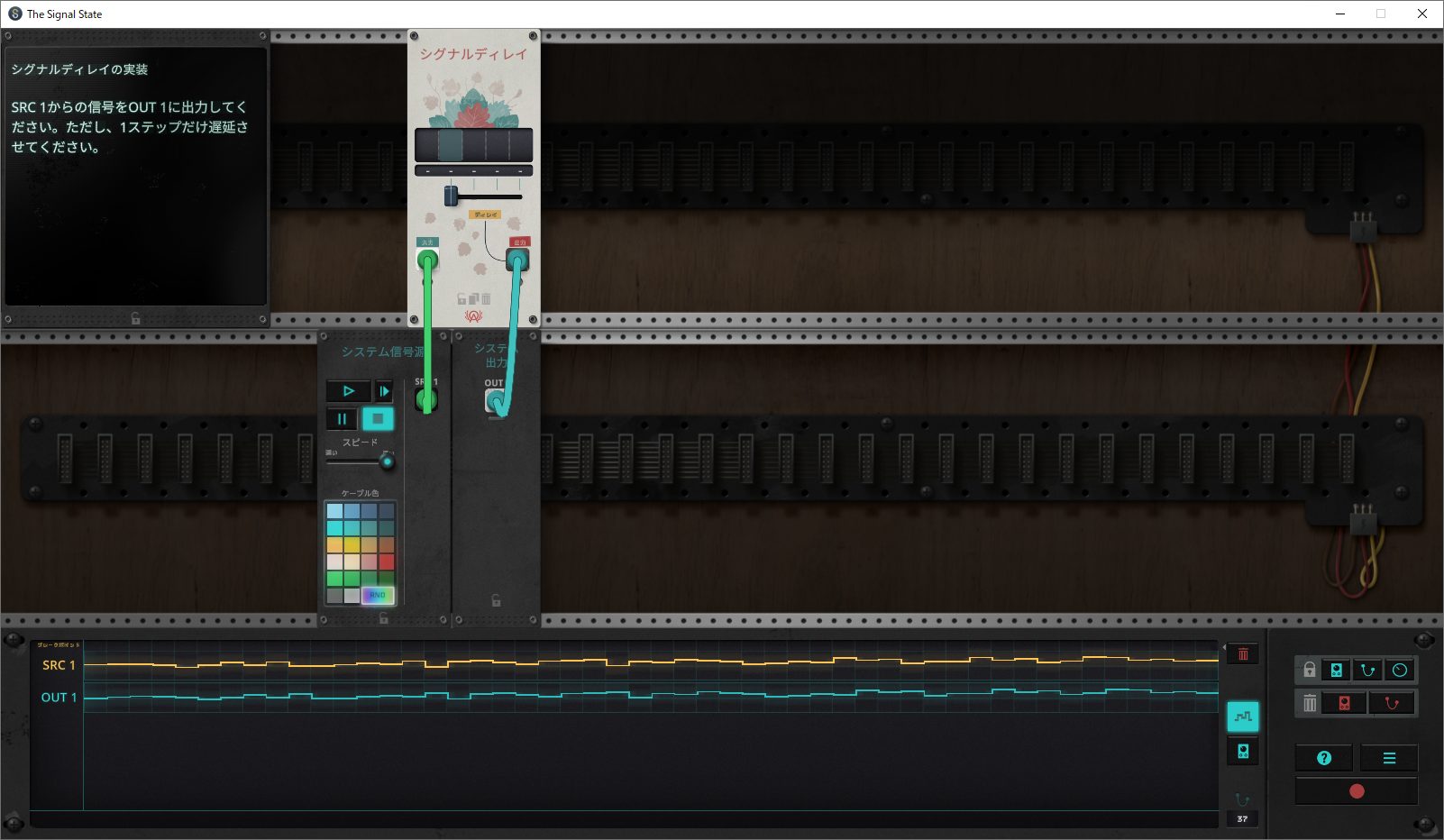

シグナルディレイの実装(Signal Delay Implementation)

SRC1からの信号をOUT1に出力してください。

ただし、1ステップだけ遅延させてください。

シグナルディレイの実装を解く

1:設計方針を検討する

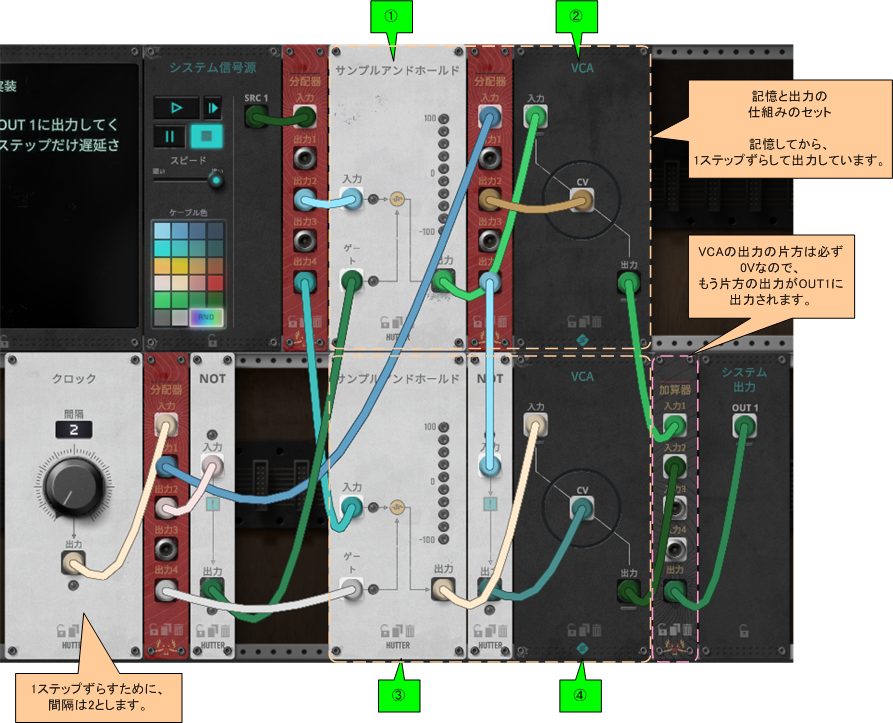

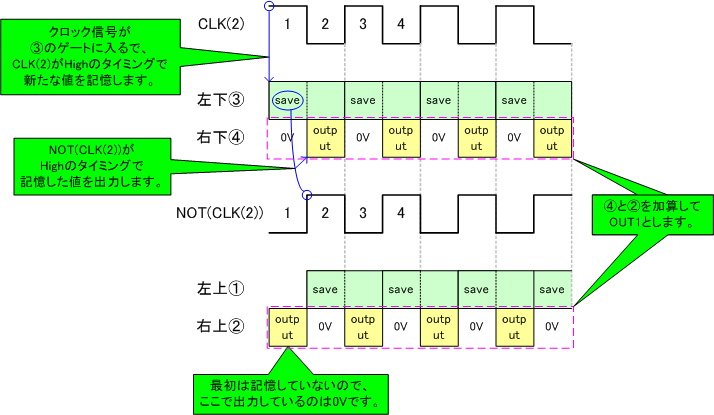

記憶と出力の仕組みをセットにした基礎回路を考えます。

記憶はサンプルアンドホールドモジュール、出力はVCAモジュールで実現できます。

「サンプルアンドホールドモジュールの出力」と「VCAモジュールの入力」は直結します。

今回はSRC1のシグナルが記憶対象なので、「サンプルアンドホールドモジュールの入力」をSRC1に接続します。

すぐ出力するのであれば「サンプルアンドホールドモジュールのゲート」と「VCAモジュールのCV」は同一ラインでよいのですが、今回のステージでは1ステップ遅延させる必要があります。

そこで、間隔2のクロックモジュールを用意します。1ステップごとに①と③に記憶させつつ、④と②から出力させるようにするのです。

つまり、基本回路を並列化します。上下のVCAから交互に出力します。VCAのCVに0Vと100Vに1ステップごとに与えることで、

「記憶した値を出力⇒0V」を繰り返させられます。

上下のCVの信号は0Vと100Vが逆転しているので、VCAの出力の片方は必ず0になります。

よって、加算器を通してOUT1につなげばよいことになります。

波形の挙動を確認してみます。

OUT1は1ステップごとに「②の出力⇒④の出力」の繰り返しになります。

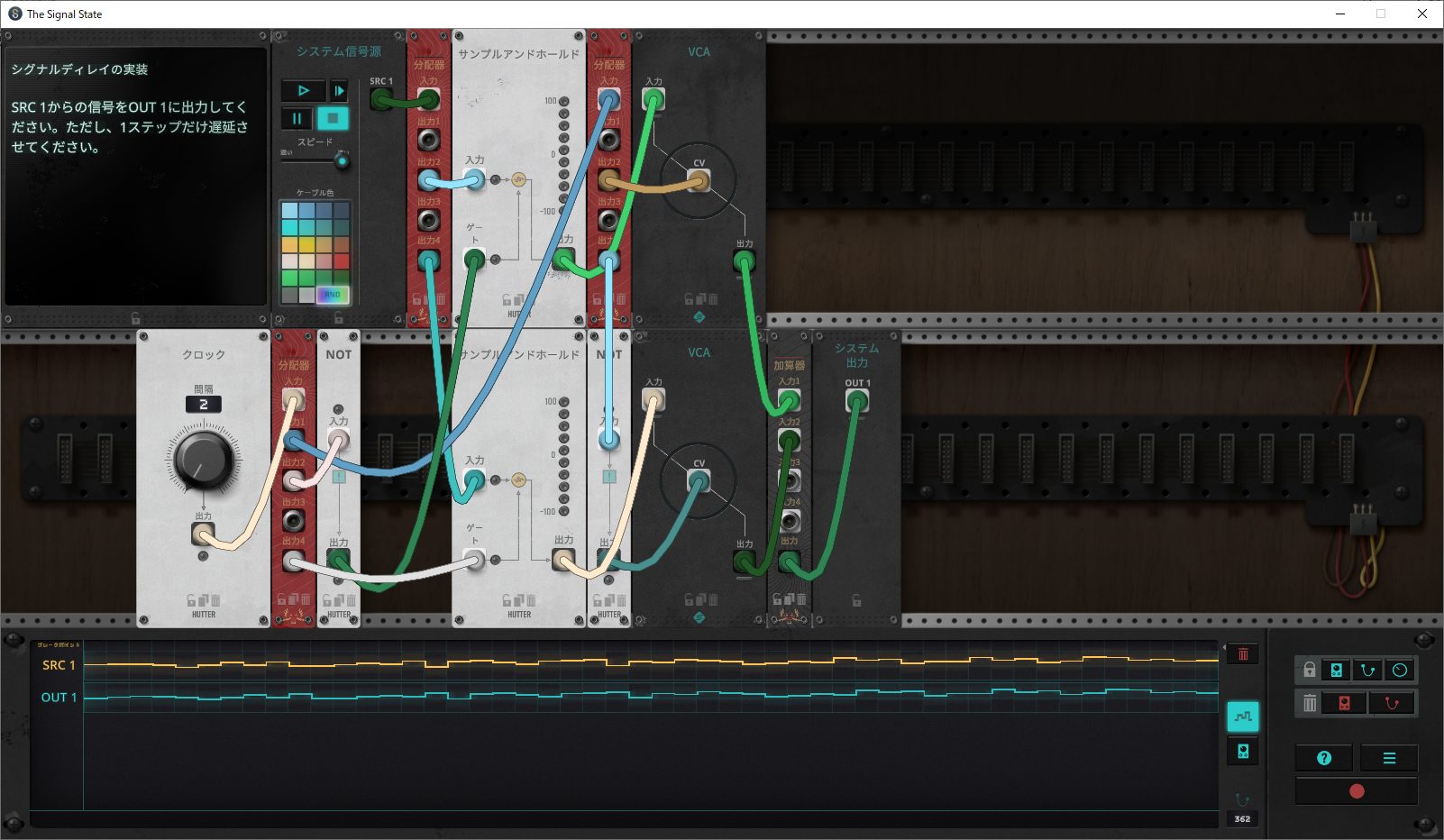

2:回路を実装する

完成した回路は次のとおりです。

論理モジュールなしで解く【別解】