Little Box【Turing Complete編】

はじめに

いつもブログをご覧いただきありがとうございます。

ミジンコに転生したIPUSIRONです😀

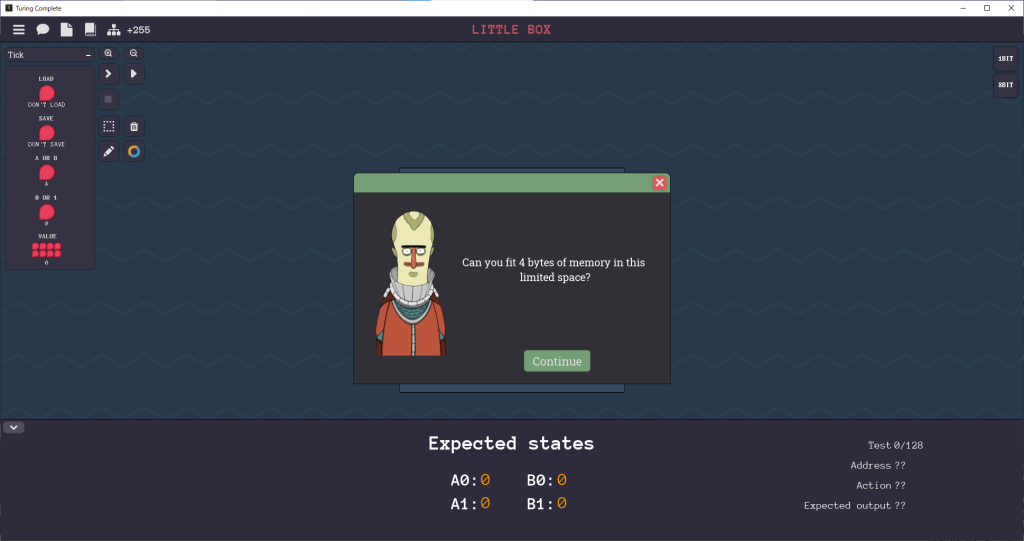

Little Boxステージ

Little Boxステージのゴールは、4バイトメモリー(2行2列のメモリーセル)を作ることです。

Little Boxステージを解く

1:コンポーネントの配置方針を考察する

1バイト(8ビット)を記憶するということは8 Bit Registerコンポーネントを使うのは明らかです。

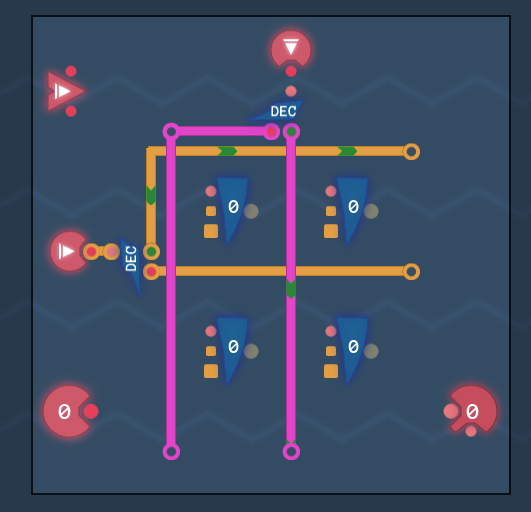

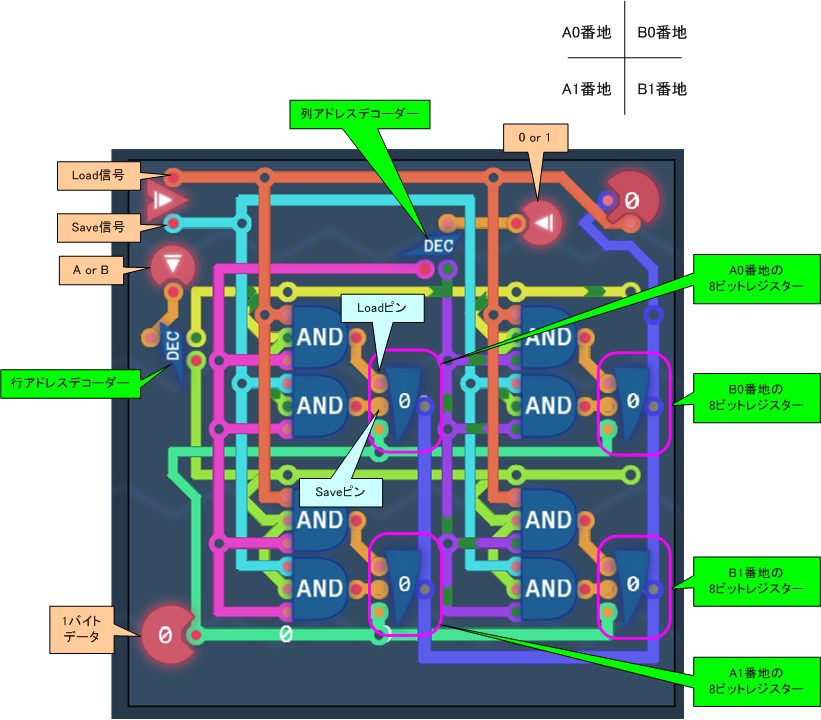

これが4個存在し、2×2に配置します。各レジスターには番地が割り当てられているものとします。

※4のメモリーセルマトリックスをイメージしています。

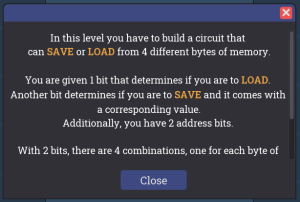

行がAとB、列が0と1です。つまり、A0、A1、B0、B1という4つの番地があり、それぞれに1つのレジスターが位置するわけです。

入力の1バイトデータを記憶する際には「番地を指定」かつ「SAVE信号をON」にします。

番地を指定するには1ビットの2入力で制御します。その先には1ビットデコーダーを接続しておけば、Hレベル・Lレベルによって、2本の出力線からHレベルのものをどちらかに切り替えれます。つまり、1ビットデコーダーをアドレスデコーダーとして働かせるわけです。

以上の内容を整理して回路を組み立てます。

ただし、まだすべての考察は終わっていないので未配線・未配置のところがあります。後で追加・調整しますので、この段階では大雑把な設計で十分です。

2:ワイヤリングを考察する

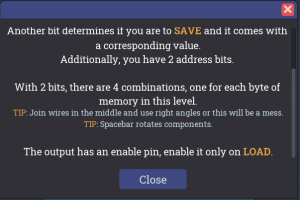

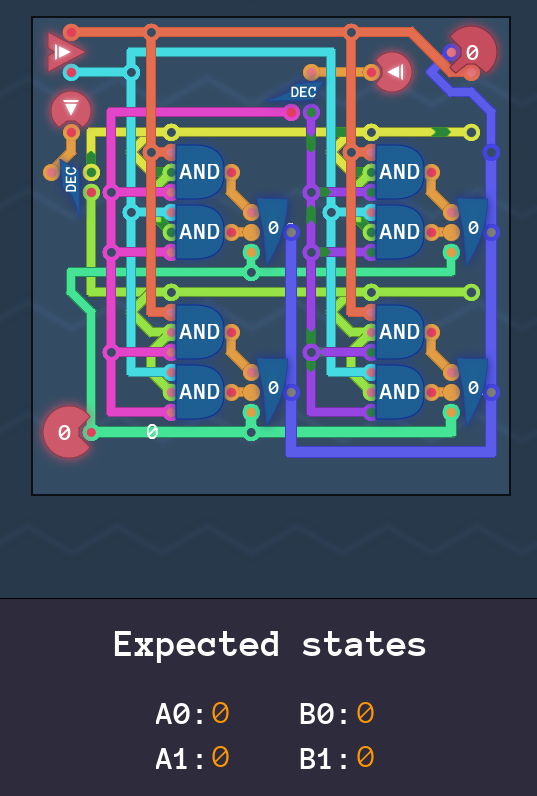

レジスターの入力にはLoadポートとSaveポートがありますが、それぞれはLittle Boxの入力のLoadとSaveにつながります。ただし、直接つなげるわけではありません。番地を確定したレジスターだけに対してLoad/Saveの制御をするので、デコーダーから行ワイヤーと列ワイヤー一緒にANDゲートを通します。つまり、3入力型ANDゲートを用います。

1つのレジスターに対して2つの(3入力型)ANDゲートが必要なので、回路全体には8つの3入力型ANDコンポーネントが登場します。

この問題の難しさは回路の複雑さよりも、狭いスペースに回路を組むことといえます。

ぎりぎり行列にきれいにレジスターを配置できたのでよいですが、これができないとワイヤリングの際にちょっと混乱するかもしれません。

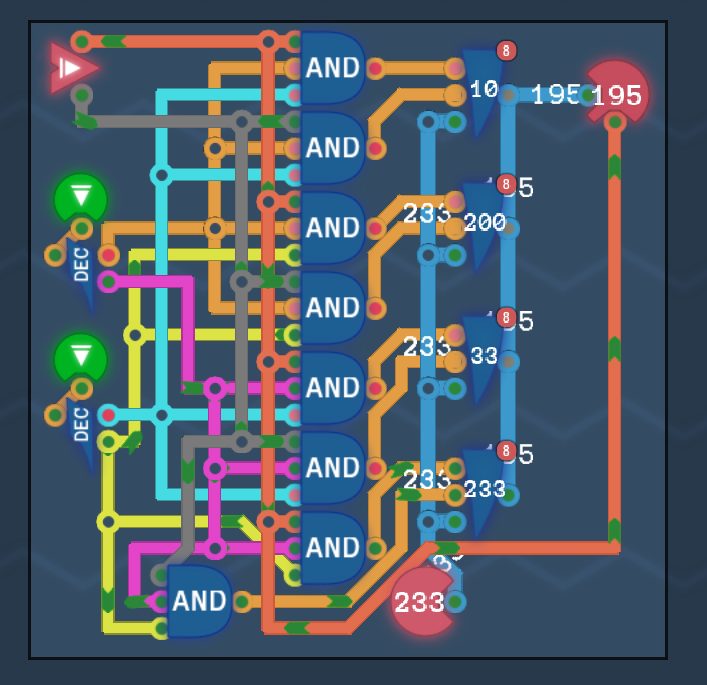

以上を踏まえて回路を組むと次のようになります。

3:テストする

クリアすると、256 Bytes Ram(256バイトバージョンのメモリー)コンポーネントがアンロックします。

※今回作ったのは4バイトメモリーですが、同様のアプローチで16行16列に拡張すれば自然に256バイトメモリーを組めます。

配置を換えたバージョン【別解】